Prof. Nuno Alves (nalves@wne.edu), College of Engineering

#### **Exam instructions:**

- 1. You have two hours to solve the proposed problem.

- 2. You can only use the class book, homework solutions or your class-notes as a reference.

- 3. You are **NOT** allowed to use any form of communication with any classmate.

- 4. There is a single problem. Once you are done with it, email <a href="mailto:nalves@wne.edu">nalves@wne.edu</a> a copy of your solution in a word document. Use the font Courier New for your report.

- 5. You do **NOT** need to give the instructor a print-out of your simulation.

- 6. You may **NOT** modify the entity portion of your code.

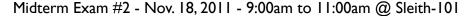

### **Question -** Design a timer capable of running from 0min:00sec to 9min:59sec.

- The circuit must have only two buttons, one which must perform the start/stop and the other which performs the circuit reset.

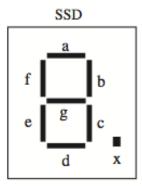

- Look at the output wave-form so you can see the expected outcomes.

- The outputs must be seven segment display (SSD) coded.

- The input CLK is a reliable 2 Hz clock signal.

- Make sure the circuit is synthesizable in hardware; for example do **NOT** initialize variables!

- You must use the following entity:

### Some useful information #I - Modulus operation

Given two positive numbers, a (the dividend) and n (the divisor), a modulo n (abbreviated as a mod n) can be thought of as the remainder, on division of a by n. For instance, the expression "5 mod 4" would evaluate to 1 because 5 divided by 4 leaves a remainder of 1, while "9 mod 3" would evaluate to 0 because the division of 9 by 3 leaves a remainder of 0; there is nothing to subtract from 9 after multiplying 3 times 3.

VHDL has a modulus operation (MOD). Assuming signal a is an integer, MOD works as follows:

a MOD 2

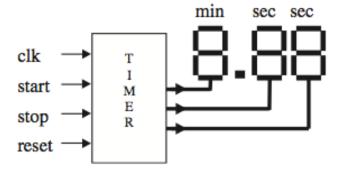

### Some useful information #2 - Seven Segment Displays SSD

A seven segment display is just a set of 7 LEDs, which becomes a 7 bit output. To write a coded zero into a seven segment display, all individual LEDS must be on, except LED g. So if the output signal was defined as:

```

signal temporary_bus: std_logic_vector (6 downto 0);

```

Then, the operation temporary\_bus <= "111110"; will make sure a zero would appear on the display. Using the same rationale temporary\_bus <= "0110000"; will write a zero.

Input: "xabcdefg"

For your convenience, here is the full list of SSD coded digits.

```

0 .... "1111110";

--7E

"0110000";

--30

2 .... "1101101";

--6D

3 .... "1111001";

--79

4 .... "0110011";

--33

5 .... "1011011";

--5B

6 .... "1011111";

--5F

7 .... "1110000";

--70

8 .... "1111111";

--7F

9 .... "1111011";

--7B

```

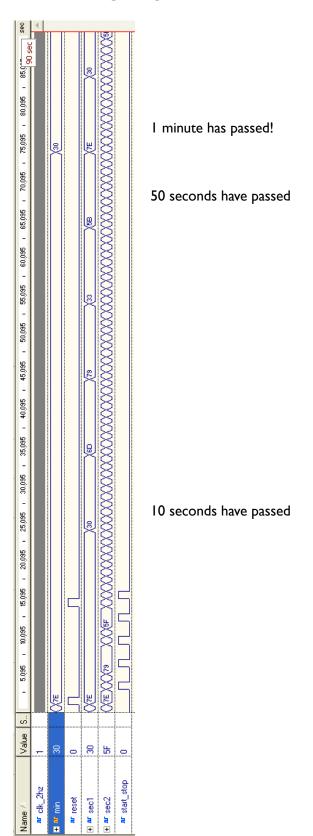

## Using the provided test-bench and running it for 20 seconds

# Using the provided test-bench and running it for 90 seconds

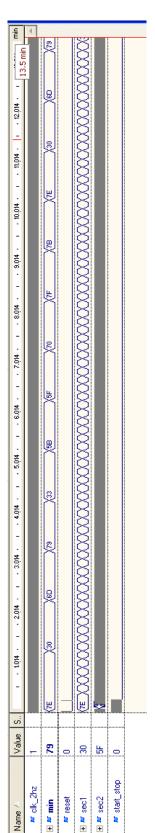

# Using the provided test-bench and running it for 810 seconds

After 9:59 minutes, the timer will reset to zero.