CPE462 - VHDL: Simulation and Synthesis - Fall'II

Prof. Nuno Alves (<u>nalves@wne.edu</u>), College of Engineering

HW #11 Solutions

Question #1:

```

library ieee;

use ieee.std logic 1164.all;

use ieee.std_logic_unsigned.all;

use ieee.std_logic_arith.all;

entity compare is

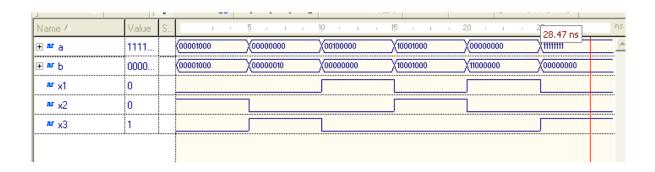

port (a,b : in std_logic_vector(7 downto 0);

sel : in std_logic;

x1,x2,x3 : out std_logic);

end entity;

architecture myarch of compare is

signal unsigned_a,unsigned_b : unsigned (7 downto 0);

signal signed_a, signed_b : signed (7 downto 0);

signal unsigned x1, unsigned x2, unsigned x3 : std logic;

signal signed x1, signed x2, signed x3 : std logic;

signal integer_a, integer_b : integer;

begin

unsigned_a <= unsigned(a);

unsigned_b <= unsigned(b);

signed a <= signed(a);

signed_b <= signed(b);</pre>

-- is a and b equal?

unsigned_x2 <= '1' when unsigned_a=unsigned_b else

'0';

signed_x2 <= '1' when signed_a=signed_b else</pre>

'0';

-- is a>b

unsigned_x1 <= '1' when unsigned_a>unsigned_b else

'0';

signed_x1 <= '1' when signed_a>signed_b else

'0';

-- is a<b

unsigned_x3 <= '1' when unsigned_a<unsigned_b else

signed_x3 <= '1' when signed_a<signed_b else</pre>

'0';

--route the appropriate signal to an the output using a mux

x1 <= unsigned x1 when sel='0' else

signed_x1;

x2 <= unsigned_x2 when sel='0' else</pre>

signed x2;

x3 <= unsigned x3 when sel='0' else

signed x3;

end architecture;

```