# CPE 462 VHDL: Simulation and Synthesis

Topic #01 - Introduction to reconfigurable computing

#### Goals of this class

#### I. Learn principles of reconfigurable computing

- 2. Master the principles of VHDL and understand its features and limitations

- 3. Acquire hands-on experience with synthesis tools, reconfigurable hardware and simulators

- 4. Strengthen engineering skills through tangible class projects that can be shown to potential employers

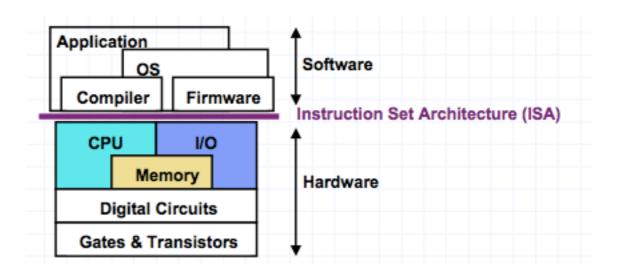

# Methods for executing computations: software

Software programmed microprocessors

#### Advantages:

Software is flexible to change

#### **Disadvantages:**

- Performance can suffer if clock is not fast

- Fixed instruction set by hardware

# Methods for executing computations: ASIC

- Straight in hardware

- Application Specific

Integrated Circuits

#### Advantages:

Extremely fast

#### **Disadvantages:**

- Algorithms can't be modified once printed

- Expensive

# Methods for executing computations: reconfigurable computing

- Fills the gap between Hardware and Software

- Individual logic gates can programed

#### Advantages:

- Higher performance than software

- More flexible than ASIC hardware

#### Disadvantages:

- Programing is not trivial

- Labor intensive development

## Reconfigurable computing approach

- I. You have a program / algorithm that you need to run in hardware

- 2. You develop that program using logic gates

- 3. You load these logic gates into a special piece of hardware

- 4. If you are unhappy with the end results, you can always modify your circuit and reload it into the same board

### Hardware description languages

We can model / simulate a piece of hardware before it is created physically!

- Unpractical to manually draw each gate in a circuit

- A hardware description language (HDL) is any language which describes the circuit's operation

- Verilog, VHDL, SystemC, Matlab Simulink, LabView, MyHDL

#### **Defining characteristics:**

- Explicit notion of time (e.g. Wait 2 ms before sending signal)

- Notations for expressing concurrency

CPE 462 - VHDL: Simulation and Synthesis - Fall 'I I Nuno Alves (nalves@wne.edu), College of Engineering

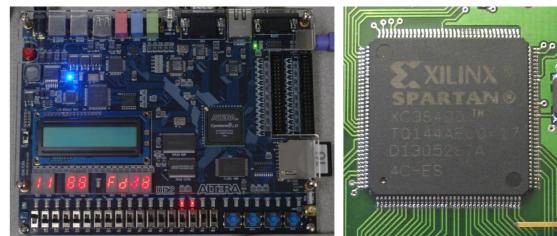

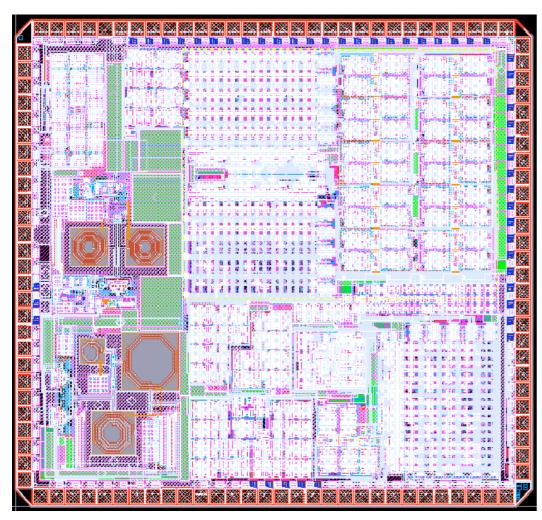

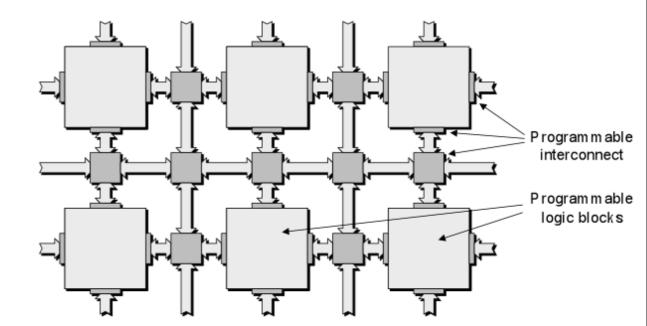

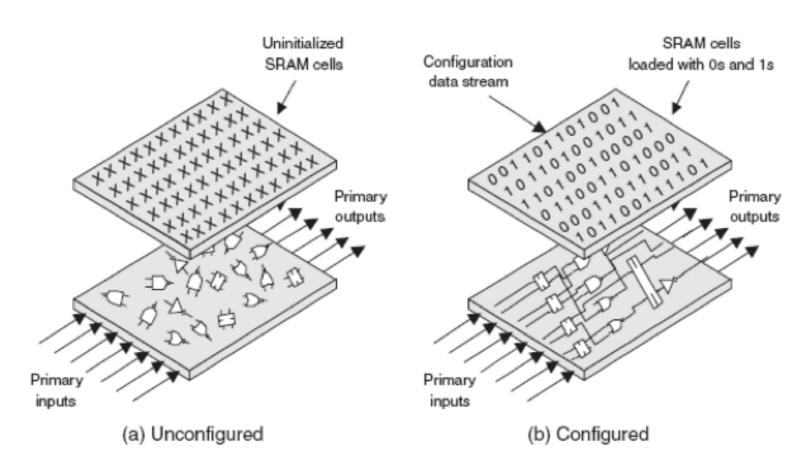

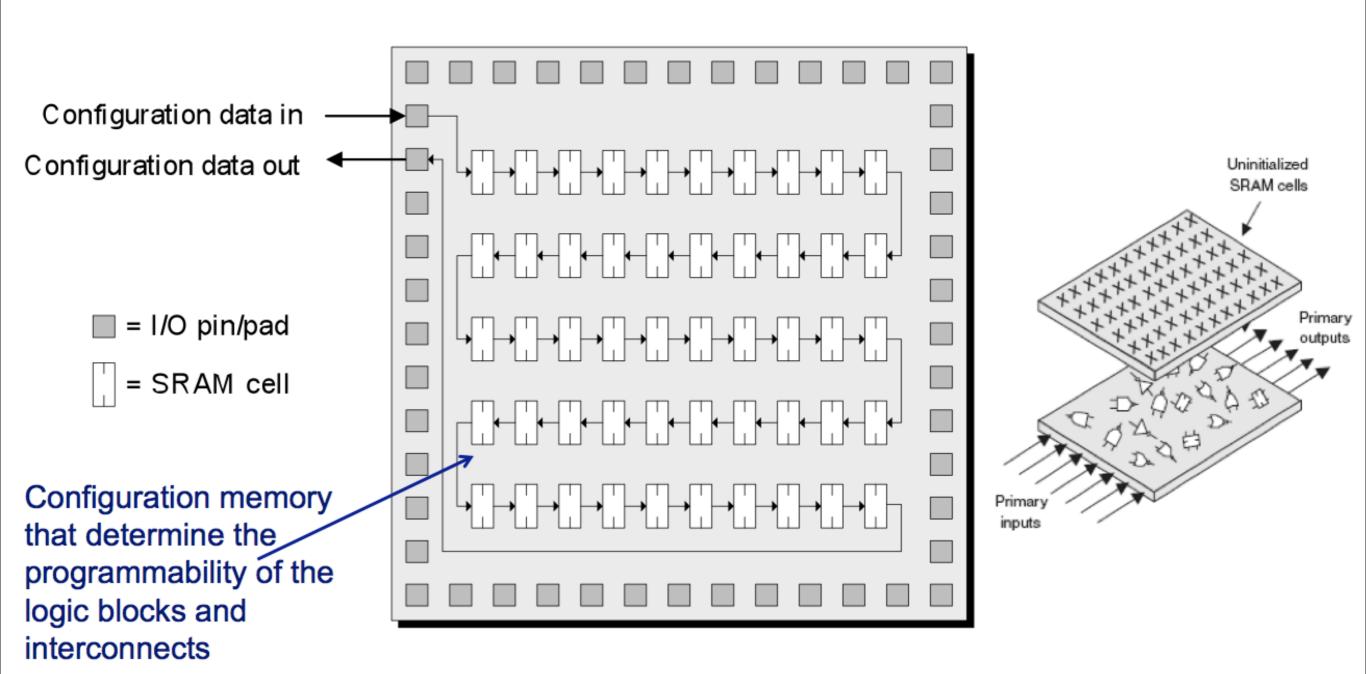

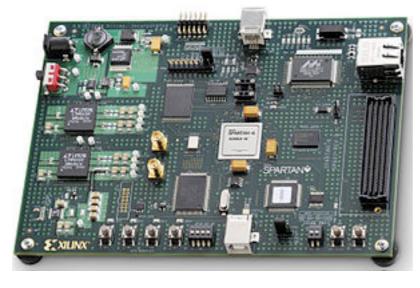

#### Reconfigurable devices

- In a reconfigurable device you configure the behavior of each logic block

- An FPGA is an example of a reconfigurable device

- FPGAs will be our VHDL prototype platform

- The logic blocks are connected by a set of routing resources that are also programmable

- Custom logic circuits can be mapped to the reconfigurable fabric

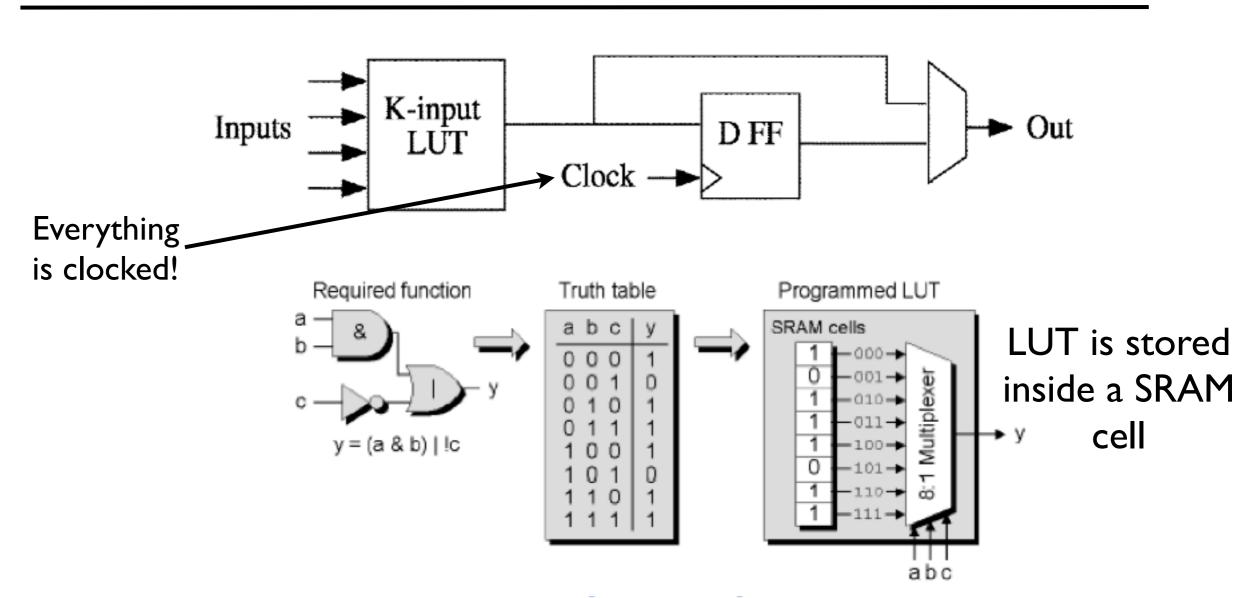

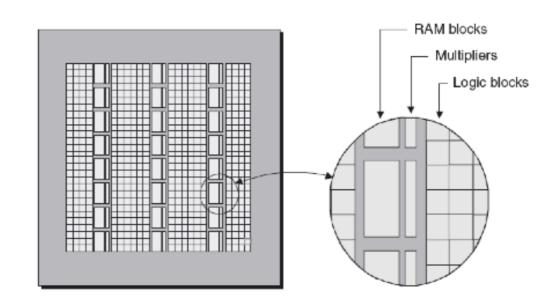

### Block logic element

- Designs need to be decomposed and mapped to logic blocks

- FPGAs might contain non-reconfigurable elements that interface to the logic blocks

## Configuring FPGAs

- FPGAs can be dynamically reprogrammed before or during runtime

- Slow to reprogram... order of seconds!

- Full or partial reconfiguration

## Why so slow to configure?

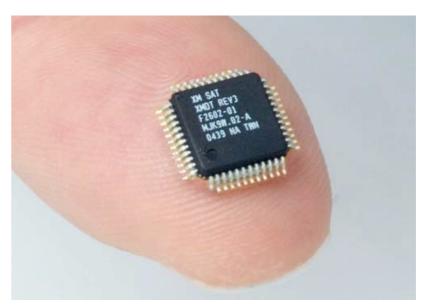

#### How does an FPGA look like?

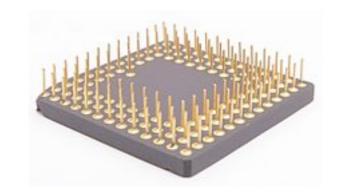

## There are several packaging types

| Туре | Dual Inline Package DIP (70's)                                                                                        | Quad Flat Package QFP<br>(80's)                  | Pin Grid Array PGA<br>(90's)                                                                                   | Ball Grid Array<br>BGA (00's)                                                              |

|------|-----------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|----------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|

| +    | <ul> <li>Easy to solder, handle</li> <li>and replace</li> <li>Extremely mature</li> <li>technology (cheap)</li> </ul> | - More available I/O<br>pins than DIP            | <ul> <li>More available I/O</li> <li>pins than QFP</li> <li>Often mounted with through hole methods</li> </ul> | <ul><li>High density</li><li>Good heat</li><li>conduction</li><li>Low inductance</li></ul> |

| -    | <ul><li>Low pin density</li><li>Signal propagates</li><li>"slowly" through pins</li></ul>                             | - No socketing or hole mounting (only soldering) | - Long leads means loss of signal integrity                                                                    | <ul><li>Expensive testing equipment</li><li>Unreliable test sockets</li></ul>              |

CPE 462 - VHDL: Simulation and Synthesis - Fall 'I I Nuno Alves (nalves@wne.edu), College of Engineering

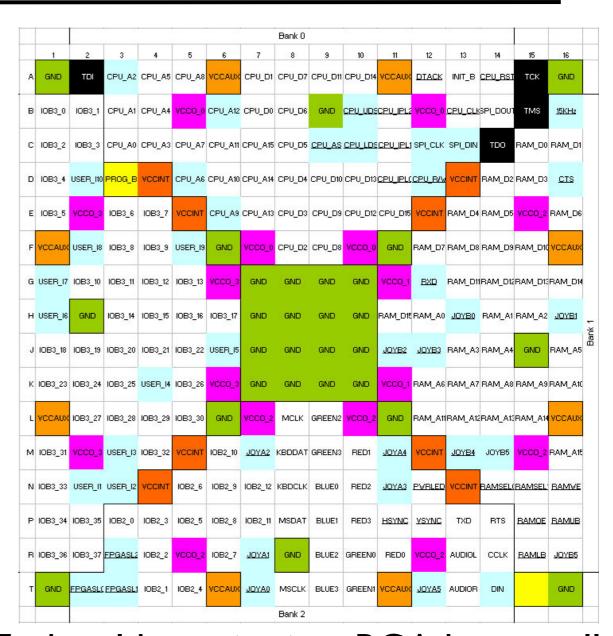

## FPGAs are mostly BGA packages

FPGA are chips with lots of I/O

With prototype boards we can fully utilize those I/O ports

Each solder point in a BGA has a well defined I/O functionality

CPE 462 - VHDL: Simulation and Synthesis - Fall 'I I Nuno Alves (nalves@wne.edu), College of Engineering

# What circuits can you implement on reconfigurable hardware?

... Besides size constraints you can deploy pretty much any circuit that has been done with standard logic gates.

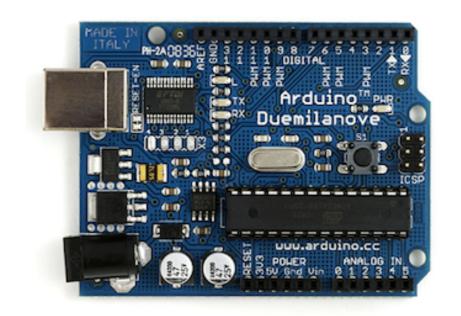

- These folks implemented an arduino compatible microprocessor in an FPGA

- Why? You can add extrafunctionality (such as extra I/O pins) to an existing micro-processor.

http://gadgetforge.gadgetfactory.net/gf/project/wiringide/

#### Embedded RAM and multipliers

- Problem: "Expensive" to implement memory with configurable logic blocks

- Solution: Add hard chunks of RAM blocks.

- Position/size vary depending on the FPGA device.

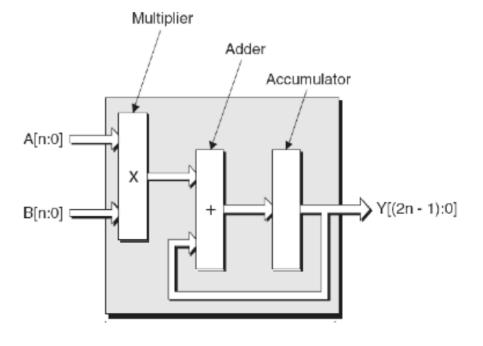

- <u>Problem</u>: Multipliers are inherently slow if cascaded

- Solution: Add hard-wired multiplier blocks

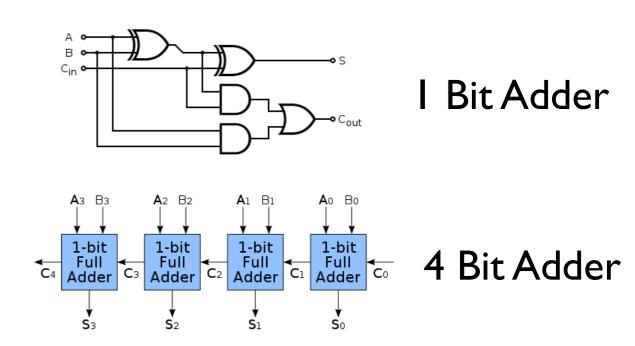

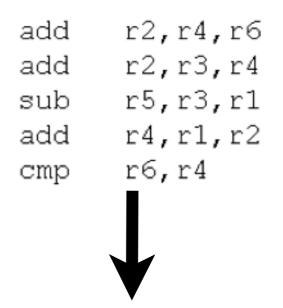

### Higher performance than software

... is obtained in many ways. For example, with spatial based computing.

Goal: I have an algorithm/program I want to run really fast.

- I) I try to extract parallelism (or concurrency) from the instructions as much as possible

- 2) Then, I implement the algorithm as hardware.

#### Spacial based execution

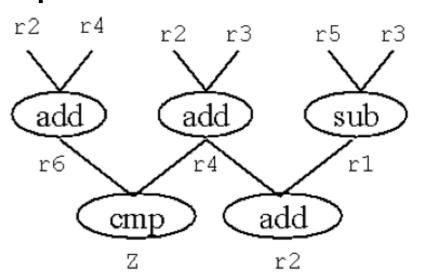

#### More flexible than ASIC

- Low/med volume IC production

- Early prototyping and logic emulation

- Accelerating algorithms in reconfigurable computing environments

- Reconfigurable functional units within a host processor (custom instructions)

- 2. Reconfigurable units used as coprocessors

- Reconfigurable units that are accessed through external I/O or a network

- Legacy Computing

# Why reconfigurable computing is more relevant these days?

- There is a demand for high-performance, data processing, computation. E.g. Gene sequencing and financial market analysis

- Why are general-purpose processors not meeting the demand?

- I. Single thread performance is no longer improving (individual core frequencies do not increase due to thermal problems)

- 2. Consume large amount of power

- Why reconfigurable architectures could meet the computational demand?

- Can process large streams of data directly in hardware

- Inexpensive and consume little power

# Tangible examples of reconfigurable computing applications

### Fast password recovery

"Using FPGA Clusters for Fast Password Recovery" - Pico Computing, Inc. (<a href="www.picocomputing.com">www.picocomputing.com</a>) - 2009 white-paper

- They take password cracking algorithms that crack SHA-1,WPA and WEP.

- Convert code into logic gates and optimize it

- Deploy the same code across a grid of reconfigurable hardware

Load protected data in memory and start process

| Recovery<br>Algorithm | PC with<br>Core™2 Duo | Pico SC3 with<br>77 FPGAs | Speed<br>Factor |

|-----------------------|-----------------------|---------------------------|-----------------|

| FileVault             | 41 minutes            | 2 seconds                 | 1230X           |

| WPA <sup>1</sup>      | 3 hours               | 11 seconds                | 981X            |

| WEP <sup>2</sup>      | 42 days (est.)        | 13 minutes                | 4,620X          |

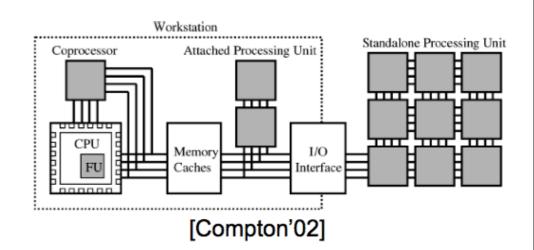

# Accurate debug and simulation of ASIC designs

- Behavioral: Entire circuit in terms of functionality (algorithm)

- Dataflow: Breaks circuits into blocks and modules

- Gate: Modules are decomposed into logic gates.

There is a lot of overlap between the design flow for an ASIC and an FPGA.

To some extent all that can be done in ASIC can be done on an FPGA.

# High frequency trading (HFT)

- •HFT is an investment technique that gets in and out of positions very quickly, while making tiny amounts on each transaction (≈ few cents)

- •If you trade a lot, and faster than your competitors, all those cents add up

- •For example, we can reduce a 30µs risk calculation on a PC, into a 3µs calculation on a FPGA

- •FPGAs are embedded into network cards to reduce any latency

|                                | Standard 10GE<br>Network card            | Low Latency<br>10GE Network<br>Card     | FPGA                      | ASIC          |

|--------------------------------|------------------------------------------|-----------------------------------------|---------------------------|---------------|

| Latency                        | 20 micros +<br>application<br>processing | 5 micros +<br>application<br>processing | 3-5 micros                | Sub-micro     |

| Ease of<br>Deployment          | Trivial                                  | Kernel driver installation              | Retraining of programmers | Specialist    |

| Man Years Effort<br>to Develop | Week                                     | Weeks                                   | 2-3 man years             | 2-3 man years |

| Elapsed Time                   | Week                                     | Weeks                                   | 6 months -year            | Year +        |

| Costs                          | \$50 - \$200                             | \$500+                                  | \$100 - \$20,000          | \$1million+   |

## Re-creating an I 980's Apple II+

http://www.cs.columbia.edu/~sedwards/apple2fpga/

The point, aside from entertainment, was to illustrate the power (or rather, low power) of modern FPGAs. (...) What made Steve Jobs his first million can now be a class project for my embedded systems class.

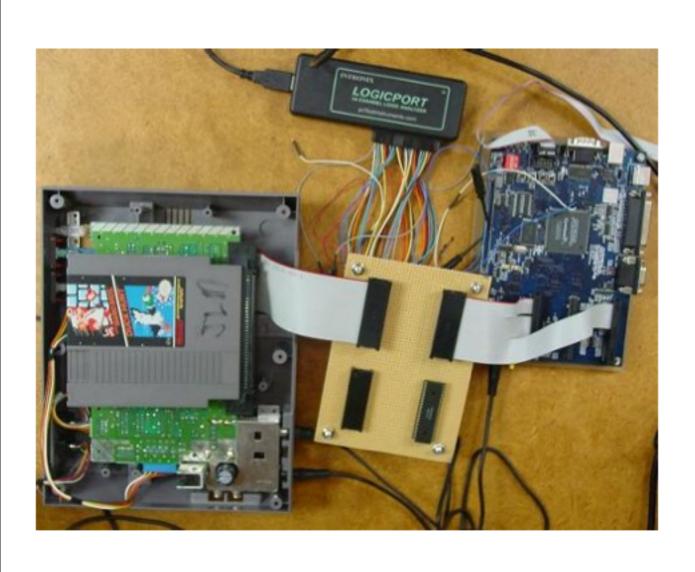

## Re-create game consoles (NES)

#### http://cegt201.bradley.edu/projgrad/proj2006/

- Dan Leach's Master's project at Bradley University

- NES is a Legacy System, still used but no longer manufactured: if one piece breaks, you are in trouble

- I year project with lots of detective work!

- Source code in VHDL is provided

# Re-create game consoles (Genesis)

http://hackaday.com/2010/07/16/sega-genesis-cloned-with-an-fpga/

- This fellow managed to re-implement a SEGA Genesis with an old FGPA board

- The onboard push buttons are used as the controller with VGA for the display

- Unfortunately source code is not provided

- For other game consoles and more info, check: http://www.fpgaarcade.com/

# What's the point of resurrecting legacy systems?

With many NES and Genesis emulators available, what is the advantage of re-creating these systems in hardware?

In other words why would you want an FPGA implementation of a legacy system?

- Replace aging, malfunctioning hardware

- Reduce power consumption by replacing a system

- Reduce the overall cost of a larger, older system

- Reduce component size and thus system size for use in smaller areas

- Safe-guard against counterfeit parts!

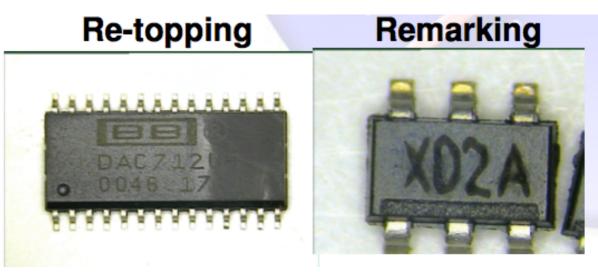

### Counterfeit parts

- "Counterfeit Electronic Parts", White paper @ Trilateral Safety and Mission Assurance Conference (2008)

- http://www.hq.nasa.gov/office/codeq/trismac/ apr08/day2/hughitt\_NASA\_HQ.pdf

Shoddy counterfeits

CPE 462 - VHDL: Simulation and Synthesis - Fall 'I I Nuno Alves (nalves@wne.edu), College of Engineering

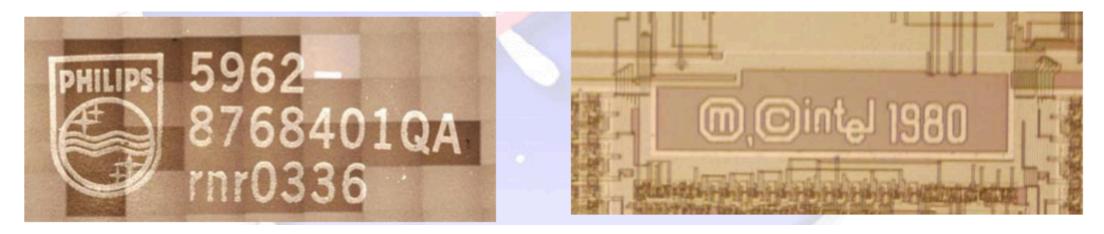

## Sophisticated counterfeiting industry

The packaging mark (outside label) does not match internal die markings!

# Hardware acceleration with GPUs

#### FPGAs vs GPUs

#### **FPGA**

- Custom chip which eliminates inefficiencies of Von Neumann execution models.

- All programming languages are hardware based.

#### **GPU**

- HW board with high memory bandwidth and allows thousands of hardware threads.

- Flexible and "easy" to program with high level languages which abstract hardware.

- NVIDIA's CUDA, AMD's CAL are new language development APIs.

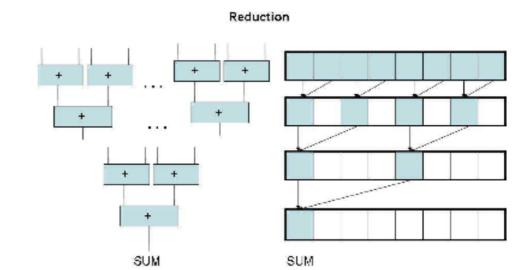

- Both extremely parallel architectures whose algorithmic speedup is based on reduction steps.

- **(Left)** FPGA with a cascade of adders of depth of log(N).

- (**Right**) Number of working threads reduces in half in each iteration of a GPU implementation of a reduce which requires log(N) iterations.

CPE 462 - VHDL: Simulation and Synthesis - Fall 'I I Nuno Alves (nalves@wne.edu), College of Engineering

#### Pro's and con's

|                           | FPGA                                                                                         | GPU                                                   |

|---------------------------|----------------------------------------------------------------------------------------------|-------------------------------------------------------|

| Development time          | Long                                                                                         | Short                                                 |

| Synchronize tasks         | Easy.We can insert hardware barriers.                                                        | Hard. API only allows synchronization of all threads. |

| Logic operations          | Logic operations  Bitwise operations: add, shift & permute done in 1 cycle.  (DES algorithm) |                                                       |

| Communication<br>Overhead | Reconfiguration takes considerable amount of time.                                           | Uses off-chip device<br>memory. PCI-Express bus.      |