# CPE 462 VHDL: Simulation and Synthesis

Topic #04 - a) Basic synthesizable data-types

# BIT (and BIT\_VECTOR)

- There are two logic levels: ('0', '1')

- Defined in Package standard of library std (no need to declare it)

#### **Declaration examples**

```

SIGNAL x: BIT;

-- x is declared as a one-digit signal

-- of type BIT.

SIGNAL y: BIT_VECTOR (3 DOWNTO 0);

-- y is a 4-bit vector,

-- with the leftmost bit being the MSB.

SIGNAL w: BIT_VECTOR (0 TO 7);

-- w is an 8-bit vector,

-- with the rightmost bit being the MSB.

```

#### **Assignment examples**

```

x <= '1';

-- x is a single-bit signal,

-- whose value is '1'. Notice that single

-- quotes (' ') are used for a single bit.

y <= "0111";

-- y is a 4-bit signal (as specified above),

-- whose value is "0111"

-- (MSB='0'). Notice that double quotes (" ")

-- are used for vectors.

w <= "01110001";

-- w is an 8-bit signal, whose value is

-- "01110001" (MSB='1').</pre>

```

CPE 462 - VHDL: Simulation and Synthesis - Fall 'I I Nuno Alves (nalves@wne.edu), College of Engineering

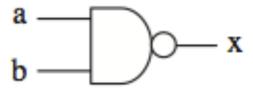

## BIT usage

```

ENTITY nand_gate IS

PORT (a, b : IN BIT;

x : OUT BIT);

END nand_gate;

ARCHITECTURE myarch OF nand_gate IS

BEGIN

x <= a NAND b;

END myarch;</pre>

```

- We've seen this before

- We take two input bits (0/1)

and we AND them together

# BIT\_VECTOR usage

- This entity+architecture has no inputs and a single output

- I declare two internal signals a&b. Think of signals as wires...

- I can manually specify the values for these signals **ONLY** because they are not inputs to my entity

| Name Value Sti  | . 20   1 · 40 · 1 · 60 · 1 · 80 · 1 · 10 100 ns |

|-----------------|-------------------------------------------------|

| <b>= </b>       | 100 13                                          |

|                 |                                                 |

| . r a(3) 0      |                                                 |

| <b>™</b> a(2) 0 |                                                 |

| лг a(1) 1       |                                                 |

| лг a(0) 1       |                                                 |

| ± Nr b F F      |                                                 |

| ± • x 3 3       |                                                 |

|                 |                                                 |

CPE 462 - VHDL: Simulation and Synthesis - Fall 'I I Nuno Alves (nalves@wne.edu), College of Engineering

```

entity main block is

port (x : out bit vector (3 downto 0));

end main block;

architecture myarch of main_block is

signal a : bit vector(3 downto 0);

signal b : bit vector(3 downto 0);

begin

a(0) \le '1';

a(1) \le '1';

a(2) <= '0';

a(3) \le '0';

-- this is the same as

--a <= "0011";

b <= "1111";

x \le a AND b;

end myarch;

```

# STD\_LOGIC (and STD\_LOGIC\_VECTOR)

- STD\_LOGIC (and STD\_LOGIC\_VECTOR): 8-valued logic system introduced in the IEEE 1164 standard

- There are several logic levels (not just '0' and '1')

- Only some logic levels are synthesizable (can be deployed in hardware)

- The ones that are not synthesizable are only intended for simulation

- We will focus mainly on the synthesizable logic levels

| Logic Level        | Synthesizable?                   |

|--------------------|----------------------------------|

| X' Forcing Unknown | (synthesizable unknown)          |

| 0' Forcing Low     | (synthesizable logic 'l')        |

| I' Forcing High    | (synthesizable logic '0')        |

| Z' High impedance  | (synthesizable tri-state buffer) |

| W'Weak unknown     | (simulation only)                |

| L' Weak Iow        | (simulation only)                |

| H'Weak high        | (simulation only)                |

| –' Don't care      | (simulation only)                |

### Start of minor detour

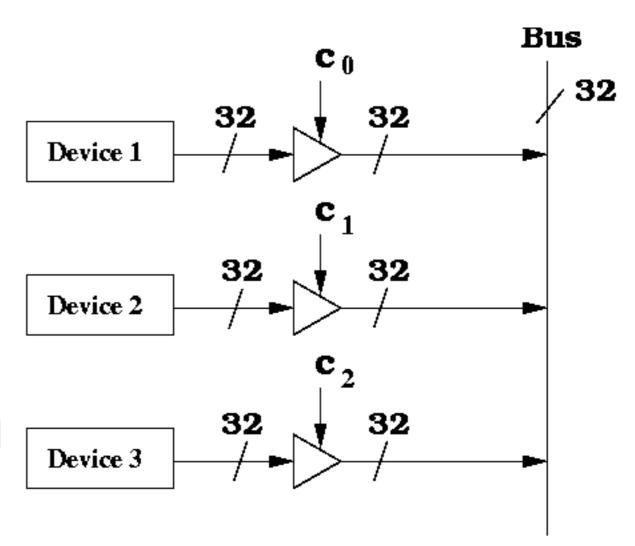

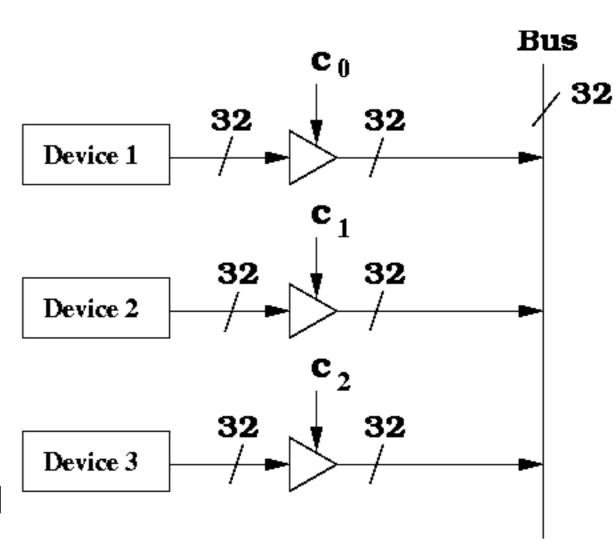

#### What is a Tri-state Buffer?

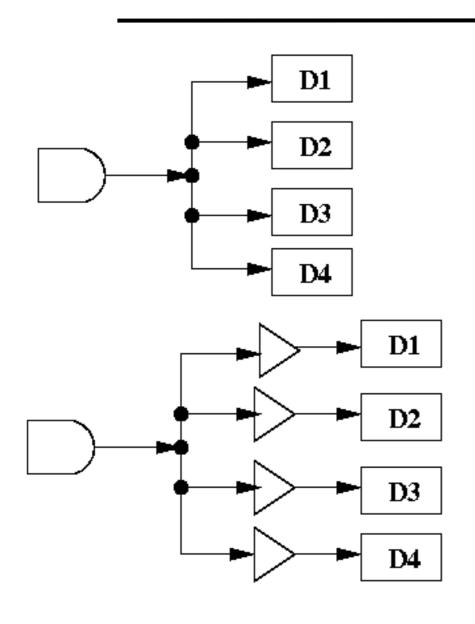

Minor digression... what is the purpose of buffers in real-designs?

- To artificially create some delay

- To increase current that a gate is feeding to other devices

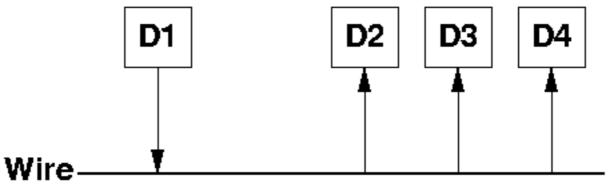

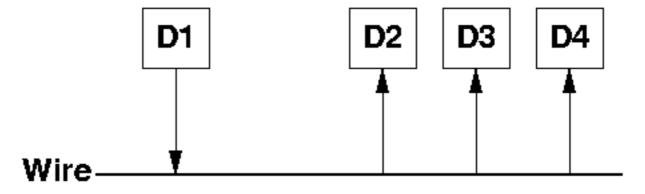

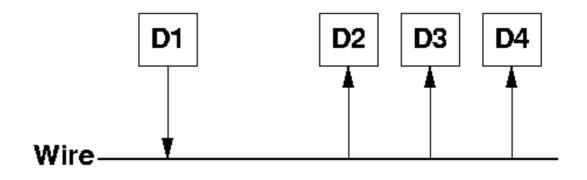

# Purpose of adding buffers

- This AND gate has a fanout of 4

- If each of the four devices gets equal current, then each device gets 1/4 of the initial current

By adding a buffer, I am boosting current to each device

Important: Why should I care about ensuring each gate gets a decent amount of current? You can't really accurately measure voltage levels if there is no current!

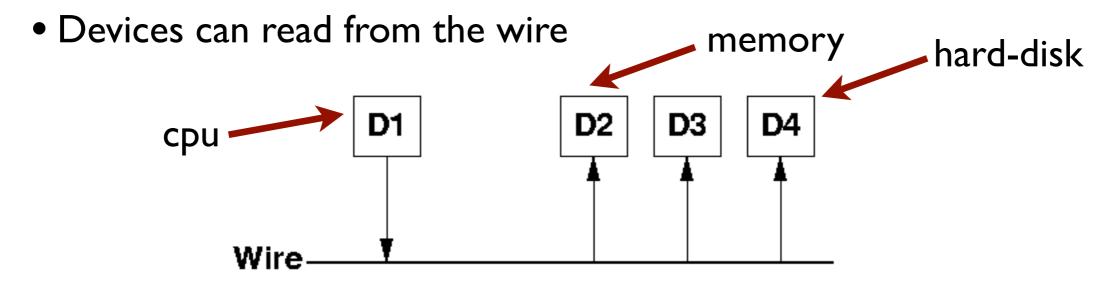

# What is High Impedance (Z)?

We can define a wire as follows:

- A piece of conductive material that allows electron flow

- A wire allows a 1-bit signal to be sent on it

- At most one device can write to a wire

- A device can write either a '0' or '1' on the wire

# Wire may connect multiple devices

- When a device writes a 'l' or '0', in reality, it is asserting a voltage, such as 0 volts for '0' and 5 volts for 'l'

- If two devices attempt to write a '0' and '1', then the wire is assumed to have a garbage value

- A device attempting to read from the wire, in such a situation, may read '0's' sometimes and read '1's' at other times

- We want to avoid two devices writing at the same time

- More than one device can read a value from a wire

# High impedance state

- If no devices write to the wire, then the wire has value Z, which stands for high impedance

- High impedance means that it is neither 0 nor 1

- If no device is writing to a wire, then reading from a wire gets an unknown value (either 0 or 1, but nothing predictable)

- A wire has no memory. That is, if you write a 1 to the wire, the wire does not store the value. The device must continuously assert a 1

#### Wire truth-table

| Device #1         | Device #2         | Output      |

|-------------------|-------------------|-------------|

| Write 0           | Write 0           | 0           |

| Write 0           | Write I           | Garbage     |

| Write I           | Write 0           | Garbage     |

| Write I           | Write I           | I           |

| Write nothing (Z) | Write 0           | 0           |

| Write nothing (Z) | Write I           | I           |

| Write nothing (Z) | Write nothing (Z) | Nothing (Z) |

Garbage as in... sometimes we read a '1' other times we read a '0'.

#### Tri-state Buffer is a control valve

- When the control input is not active, the output is "Z"

- The "valve" is open, and no electrical current flows through

- Thus, even if x is 0 or 1, that value does not flow through

| С | in | out |

|---|----|-----|

| 0 | 0  | Z   |

| 0 | I  | Z   |

| I | 0  | 0   |

| I | I  | I   |

# Why tri-state buffers?

- A common way for many devices to communicate with one another is on a bus

- That a bus should only have one device writing to it, although it can have many devices reading from it

- Since many devices always produce output (such as registers) and these devices are hooked to a bus, we need a way to control what gets on the bus, and what doesn't.

#### Tri-state buffers vs MUX

- Who cares? Why don't I replace these three state buffers with a MUX?

- With a MUX we're guaranteed only one device makes it to the bus.

- What if we don't want any devices to make it to the bus?

- One solution is to add an enable input to a MUX. Only when the enable is active, the output is selected from one of the inputs.

## End of minor detour

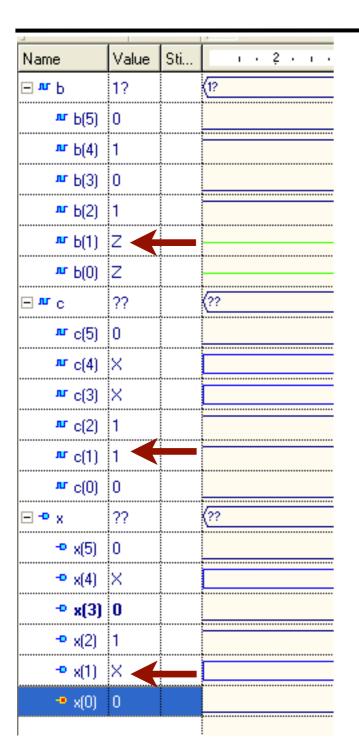

## STD\_LOGIC\_VECTOR usage

In order to use

STD\_LOGIC\_VECTOR or

STD\_LOGIC you **MUST**add this library

Since b and c are internal wires I force their initial values this way

```

library ieee;

use ieee.std_logic_1164.all;

entity main_block is

port (x : out std_logic_vector(5 downto 0));

end main_block;

architecture myarch of main_block is

signal b : std_logic_vector(5 downto 0):= "0101ZZ";

signal c : std_logic_vector(5 downto 0):= "0XX110";

begin

x <= b AND c;

end myarch;</pre>

```

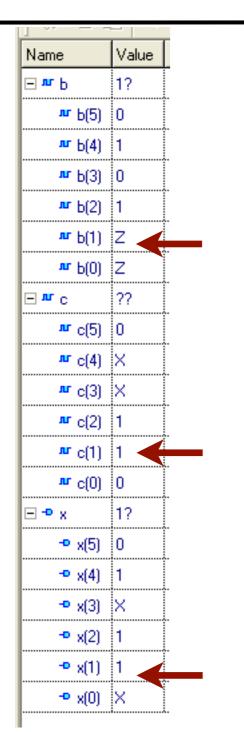

## STD\_LOGIC\_VECTOR

```

library ieee;

use ieee.std_logic_1164.all;

entity main_block is

port (x : out std_logic_vector(5 downto 0));

end main_block;

architecture myarch of main_block is

signal b : std_logic_vector(5 downto 0):= "0101ZZ";

signal c : std_logic_vector(5 downto 0):= "0XX110";

begin

x <= b AND c;

end myarch;</pre>

```

### STD\_LOGIC\_VECTOR

```

library ieee;

use ieee.std_logic_1164.all;

entity main_block is

port (x : out std_logic_vector(5 downto 0));

end main_block;

architecture myarch of main_block is

signal b : std_logic_vector(5 downto 0):= "0101ZZ";

signal c : std_logic_vector(5 downto 0):= "0XX110";

begin

x <= b OR c;

end myarch;</pre>

```

# Boolean logic with unknowns (X)

#### X can be 0 or 1

If A=0 and B=X

0 AND 0 = 0

0 AND I = 0

0 OR 0 = 0

0 OR I = I

If A=I and B=X

IAND0=0

I AND I = I

I OR 0 = I

I OR I = I

| Α | В | A and B | A or B | A xor B |

|---|---|---------|--------|---------|

| 0 | X | 0       | X      | X       |

| I | X | X       |        | X       |

If A=0 and B=X

A AND B is always 0, because the value of B can never alter the result

If A=I and B=X

A OR B is always I, because the value of B can never alter the result

# Boolean logic with high impedance (Z)

#### Z can be 0 or 1 or neither

If A=0 and B=Z

0 AND 0 = 0

0 AND I = 0

0 AND neither = 0

0 OR 0 = 0

0 OR I = I

0 OR neither = 0

| A | В | A and B | A or B | A xor B |

|---|---|---------|--------|---------|

| 0 | Z | 0       | X      | X       |

| I | Z |         |        |         |

# Boolean logic with high impedance (Z)

#### Z can be 0 or 1 or neither

If A=I and B=Z

IAND0=0

IANDI=I

I AND neither = I

I OR 0 = I

I OR I = I

I OR neither = I

| A | В | A and B | A or B | A xor B |

|---|---|---------|--------|---------|

| 0 | Z | 0       | X      | X       |

| I | Z | X       |        | X       |

# Other synthesizable VHDL data types

- BOOLEAN: True, False

- INTEGER: 32-bit integers (from -2,147,483,647 to +2,147,483,647)

- NATURAL: Non-negative integers (from 0 to +2,147,483,647)

- SIGNED and UNSIGNED: data types defined in the std\_logic\_arith package of the ieee library. They have the appearance of STD\_LOGIC\_VECTOR, but accept arithmetic operations, which are typical of INTEGER data types

# Assignment examples

| x0 <= '0';        | bit, std_logic, or std_ulogic value '0'                                         |

|-------------------|---------------------------------------------------------------------------------|

| x1 <= "00011111"; | <pre>bit_vector, std_logic_vector, std_ulogic_vector, signed, or unsigned</pre> |

| x4 <= B"101111"   | binary representation of decimal 47                                             |

| x5 <= 0"57"       | octal representation of decimal 47                                              |

| x6 <= X"2F"       | hexadecimal representation of decimal 47                                        |

| n <= 1200;        | integer                                                                         |

| m <= 1_200;       | integer, underscore allowed                                                     |

| IF ready THEN     | Boolean, executed if ready=TRUE                                                 |

# Full code examples

Useless entity, but exemplifies how we can declare internal signals with some initial values.

```

library ieee;

use ieee.std_logic_1164.all;

entity main_block is

end main_block;

architecture myarch of main_block is

signal x0 : std_logic :='0';

signal x5 : std_logic_vector(5 downto 0):= O"57";

signal x6 : std_logic_vector(7 downto 0):= X"2F";

signal n : integer := 1200;

signal m : integer := 1_200;

signal ready : boolean := true;

begin

end myarch;

```

# Full code examples

Same outcome as the previous slide, but signals are initialized inside the architecture begin/end block.

```

library ieee;

use ieee.std_logic_1164.all;

entity main_block is

end main block;

architecture myarch of main block is

signal x0 : std logic;

signal x5 : std_logic_vector(5 downto 0);

signal x6 : std logic vector(7 downto 0);

signal n : integer;

signal m : integer;

signal ready: boolean;

begin

x0 <= '0';

x5 <= 0"57";

x6 <= X"2F";

<= 1200;

m <= 1 200;

ready <= true;

end myarch;

```

# Legal or Illegal?

```

A good way to confirm

SIGNAL a: BIT;

these, is to try to compile

SIGNAL b: BIT VECTOR(7 DOWNTO 0);

this code in active HDL.

SIGNAL c: STD LOGIC;

SIGNAL d: STD_LOGIC_VECTOR(7 DOWNTO 0);

SIGNAL e: INTEGER RANGE 0 TO 255;

a <= b(5); -- legal (same scalar type: BIT)</pre>

b(0) <= a; -- legal (same scalar type: BIT)

c <= d(5); -- legal (same scalar type: STD_LOGIC)</pre>

d(0) <= c; -- legal (same scalar type: STD_LOGIC)</pre>

a <= c; -- illegal (type mismatch: BIT x STD LOGIC)</pre>

b <= d; -- illegal (type mismatch: BIT VECTOR x</pre>

-- STD LOGIC VECTOR)

e <= b; -- illegal (type mismatch: INTEGER x BIT_VECTOR)

-- illegal (type mismatch: INTEGER x

e <= d;

-- STD LOGIC VECTOR)

```

### Practice Exercises

# Exercise #1- Legal or Illegal Assignments?

& means append!

I) Look at these signals...Which are the legal assignments? Why?

```

SIGNAL a: STD_LOGIC;

SIGNAL b: BIT;

SIGNAL x: byte;

SIGNAL y: STD_LOGIC_VECTOR (7 DOWNTO 0);

SIGNAL v: BIT_VECTOR (3 DOWNTO 0);

SIGNAL z: STD_LOGIC_VECTOR (: 7 DOWNTO 0);

```

Not sure about some of these? Use Active HDL to check.

```

z <= "11111" & "000";

x(2) \le a;

b \le a;

y(5 \text{ TO } 7) \le z(6 \text{ DOWNTO } 0);

y(0) \le x(0);

y \le ('1','1','1','1','1','1','0','Z');

x \le "111111110";

z \ll y;

b \le v(3);

y(2 DOWNTO 0) \le z(6 DOWNTO 4);

x \ll y;

z(7) \le x(5);

```

# Exercise #2- What is the difference between these two implementations

```

ENTITY and2 IS

PORT (a, b: IN BIT;

x: OUT BIT);

END and2;

ARCHITECTURE and2 OF and2 IS

BEGIN

x <= a AND b;

END and2;

ENTITY and2 IS

PORT (a, b: IN BIT_VECTOR (0 TO 3);

x: OUT BIT_VECTOR (0 TO 3));

END and2;

END and2;

END and2;

END and2 IS

BEGIN

x <= a AND b;

END and2;

END and2;

```

Draw the inferred circuit from each code snippet.