## CPE 462 VHDL: Simulation and Synthesis

Topic #04 - b) Types and arrays

## Types

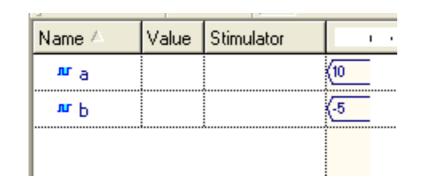

## User defined data-types (integer)

- In VHDL we can define our own data types amongst integers and enumerations

- For example, I want an integer that can only take values from -32 to 32

```

type my_integer is range -32 to 32

```

Full source code example on how you would use it...

```

entity test is

end entity;

architecture myarch of test is

type my_integer is range -32 to 32;

signal a : my_integer;

signal b : my_integer;

begin

a <= 10;

b <= -5;

end architecture;</pre>

```

WESTERN NEW ENGLAND

UNIVERSITY

CPE 462 - VHDL: Simulation and Synthesis - Fall 'I I Nuno Alves (nalves@wne.edu), College of Engineering

#### This will not compile

```

entity test is

end entity;

architecture myarch of test is

type my integer is range -32 to 32;

signal a: my integer;

signal b : my_integer;

begin

a <= 10;

b <= -50;

end architecture;

acom -work test $DSN/src/main.vhd

# Compile...

# File: c:\cpe462\test\test\src\main.vhd

# Compile Entity "test"

" # Compile Architecture "myarch" of Entity "test"

# Error: COMP96_0368: main.vhd : (10, 7): Value -50 out of range.

# Compile failure 1 Errors O Warnings Analysis time: 0.0 [s]

```

#### This will also not compile

```

1   entity test is

2   end entity;

3

4   architecture myarch of test is

5        type myrange is range 0 to 10;

6        signal a : myrange := 10;

7        signal b : myrange := 5;

8        signal c : myrange;

9   begin

10

11        c <= a AND b;

12

13   end architecture;

14

15</pre>

```

You can't have logic operations on integer user defined data-types

## User defined data-types (enumerated)

- For example, I want an enumeration of the mood of my robot

- The robot can only be "confused", "sad" or "happy"

```

type robot_mood is (confused, sad, happy)

```

Full source code example on how you would use it...

```

Name A Value Stimulator 1 · 2 · 1 · 4 · 1 · 6

nr a Sad

nr b (happy

```

```

entity test is

end entity;

architecture myarch of test is

type robot_mood is (confused, happy, sad);

signal a : robot_mood;

signal b : robot_mood;

begin

a <= sad;

b <= happy;

end architecture;</pre>

```

# Why do we care about enumerated data-types?

- It may make your code a lot more readable.

- For example:

- Useful to describe finite state machines:

- TYPE state IS (idle, forward, back, stop);

- Useful to describe colors:

- TYPE color IS (red, green, blue);

You can't perform logic operations with enumerations

```

1  entity test is

2  end entity;

3

4  architecture myarch of test is

5     type color is (red, green, blue);

6     signal colorA : color;

7     signal colorB : color;

8     signal mixedColor : color;

9  begin

10

11     mixedColor <= colorA AND colorB;

12

13  end architecture;

14

15</pre>

```

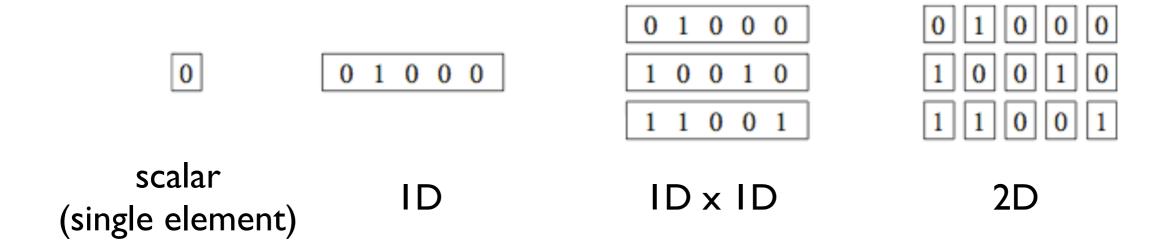

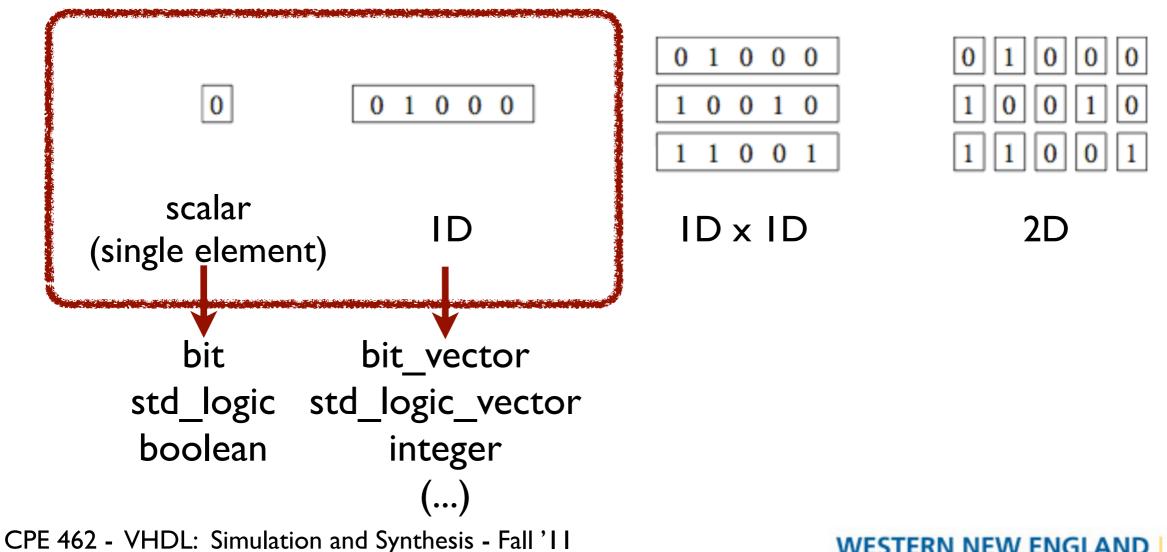

## Arrays

#### Structure of arrays

- Arrays are collections of objects of the same type

- They can be one-dimensional (ID), two-dimensional (2D), or one-dimensional-by-one-dimensional (IDxID)

#### Structure of pre-defined data types

The pre-defined VHDL data types include only the scalar (single bit) and vector (one-dimensional array of bits) categories.

Nuno Alves (nalves@wne.edu), College of Engineering

### Creating a ID x ID array

```

0

1

0

0

0

1

0

0

1

0

1

1

0

0

1

```

- ID x ID arrays are useful to store groups of bits (e.g. a ROM)

- In order to create an array we need two steps

To specify a new array type:

```

TYPE type_name IS ARRAY (specification) OF data_type;

```

To make use of the new array type:

```

SIGNAL signal_name: type_name [:= initial_value];

```

## ID x ID array example

- 0

1

0

0

0

1

0

0

1

0

1

1

0

0

1

- row 0

- We want array with four vectors, each of size eight bits

- Each vector is named "row"

- Entire array is named "matrix"

| Name △          | Value | Stimulator | 1 . 2 . 1 . 4 . 1 . 6 . 1 . |

|-----------------|-------|------------|-----------------------------|

| ⊟ nr x          | (08,1 |            | (08,12,19)                  |

| <b>⊕ №</b> x(2) | 08    |            | (08                         |

| ⊡ <b>™</b> x(1) | 12    |            | (12                         |

| ъ               | 1     |            |                             |

| л               | 0     |            |                             |

| л               | 0     |            |                             |

| ъ               | 1     |            |                             |

| ъ               | 0     |            |                             |

| = <b>n</b> ×(0) | 19    |            | (19                         |

| лг              | 1     |            |                             |

| лг              | 1     |            |                             |

| лг              | 0     |            |                             |

| лг              | n     |            |                             |

CPE 462 - VHDL: Simulation and Synthesis - Fall 'I I Nuno Alves (nalves@wne.edu), College of Engineering

```

library ieee;

use ieee.std_logic_1164.all;

entity test is

end entity;

architecture myarch of test is

-- 1D array

type row is array (4 downto 0) of std logic;

-- 1Dx1D array

type matrix is array (2 downto 0) of row;

-- 1Dx1D signal

signal x: matrix;

begin

x(0) \le "11001";

x(1) \le "10010";

x(2) \le "01000";

end architecture;

```

and architecture;

# ID x ID Array simplification

```

0

1

0

0

1

0

0

1

0

1

1

0

0

1

```

## Another way to initialize arrays 10 10

```

0 1 0 0 0

```

```

library ieee;

use ieee.std_logic_1164.all;

this is how you do it...

entity test is

end entity;

architecture myarch of test is

type matrix is array (2 downto 0) of std logic vector (4 downto 0);

signal x: matrix := ( "01000", "10010", "11001");

begin

all this is commented out!

--x(0) \le "11001";

--x(1) \le "10010";

--x(2) \le "01000";

end architecture;

```

#### Even another way

```

library ieee;

use ieee.std_logic_1164.all;

entity test is

end entity;

architecture myarch of test is

type matrix is array (2 downto 0) of std_logic_vector(4 downto 0);

signal x: matrix := ( ('0','1','0','0','0'), "10016", "11001");

begin

--x(0) <= "11001";

--x(1) <= "10010";

--x(2) <= "01000";

end architecture;</pre>

```

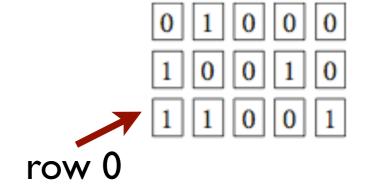

#### Constant array

```

row 0

```

```

if you want unmodifiable

library ieee;

use ieee.std_logic_1164.all;

data in your array, replace

signal with constant

entity test is

end entity;

architecture march of test is

type matrix is array (2 downto 0) of std logic vector(4 downto 0);

constant x: matrix := ( "01000", "10010", "11001");

begin

all this is commented out!

--x(0) \le "11001";

--x(1) \le "10010";

--x(2) \le "01000";

end architecture;

```

#### Lets get some data

```

row 0

```

```

library ieee;

use ieee.std_logic_1164.all;

entity test is

end entity;

architecture myarch of test is

type matrix is array (2 downto 0) of std_logic_vector(4 downto 0);

signal x: matrix := ( "01000", "10010", "11001");

signal y : std_logic_vector(4 downto 0);

begin

y \le x(1);

end architecture;

```

creating a new signal bus assigning one matrix row to to this new bus

## Now with input stimulus!

```

0

1

0

0

0

1

0

0

1

0

1

1

0

0

1

```

row 0

```

library ieee;

use ieee.std_logic_1164.all;

entity test is

port (a : in std_logic_vector(1 downto 0);

output : out std_logic_vector(4 downto 0));

end entity;

this

architecture myarch of test is

type matrix is array (2 downto 0) of td_logic_vector(4 downto 0);

signal x: matrix := ( "01000", "10010", "11001");

```

We haven't studied in detail "processes" and "if statements"... but this is an example!

```

| could begin

```

| Name /        | Value | Stimulator     | 1 · 20 · 1 · 40 40 ns  |

|---------------|-------|----------------|------------------------|

| ⊟ ► a         | 0     | Binary Counter |                        |

| <b>P</b> a(1) | 0     |                |                        |

| <b>P</b> a(0) | 0     |                |                        |

| = · output    | 19    |                | (19 \(12 \)\(08 \)\(ZZ |

| output(4)     | 1     |                |                        |

| output(3)     | 1     |                |                        |

| output(2)     | 0     |                |                        |

| output(1)     | 0     |                |                        |

| output(0)     | 1     |                |                        |

end architecture;

CPE 462 - VHDL: Simulation and Synthesis - Fall 'I I Nuno Alves (nalves@wne.edu), College of Engineering

#### 2D Array

Its construction is not based on vectors, but rather entirely on scalars

# Extracting data on 2D Array

```

library ieee;

use ieee.std logic 1164.all;

entity test is

end entity;

architecture myarch of test is

type matrix2D is array (0 TO 2, 4 DOWNTO 0) of std_logic;

signal x : matrix2D := (

('1','1','0','0','1'),

('1','0','0','1','0'),

('0','1','0','0','0')

);

creating a new scalar

signal y : std_logic;

(row, column)

begin

y \le x(2,4);

end architecture;

```

| Name A         | Value | S        | 1 . 2 . 1 |

|----------------|-------|----------|-----------|

|                | -     | _        |           |

| ⊒ <sub>1</sub> | 6648  | <u> </u> | (6648     |

| лг x(0,4)      | 1     |          |           |

| ™ x(0,3)       | 1     |          |           |

| ™ x(0,2)       | 0     |          |           |

| ™ x(0,1)       | 0     |          |           |

| м x(0,0)       | 1     |          |           |

| иг х(1,4)      | 1     |          |           |

| м х(1,3)       | 0     |          |           |

| лг х(1,2)      | 0     |          |           |

| м х(1,1)       | 1     |          |           |

| м x(1,0)       | 0     |          |           |

| лг х(2,4)      | 0     |          |           |

| иг х(2,3)      | 1     |          |           |

| лг х(2,2)      | 0     |          |           |

| лг x(2,1)      | 0     | <u> </u> |           |

| лг x(2,0)      | 0     | <br>!    |           |

| w y            | 0     |          |           |

|                |       | ^        |           |

#### Neat Active HDL feature

#### Change signal display types

## Signed / unsigned data types

#### What for?

- This type is used for arithmetic functions!

- An UNSIGNED value is a number never lower than zero

- "0101" represents the decimal 5

- "1101" signifies 13

- A SIGNED value can be positive or negative (in 2's complement)

- "0101" represents the decimal 5

- "I I 0 I" signifies 3

#### 2's Complement

- Suppose we're working with 8 bit quantities

- We want to find -28 in two's complement.

- 1. First we write out 28 in binary form: 00011100

- 2. Then we invert each digits: III00011

- 3. Then we add 1:11100100

- That is how one would write -28 in 8 bit binary

#### How to use?

- You need to add the std\_logic\_arith library to your program

- Syntax is as follows:

- SIGNAL x: SIGNED (7 DOWNTO 0);

- SIGNAL y: UNSIGNED (0 TO 3);

#### **Arithmetic operators!**

```

+ Addition

```

Subtraction

Multiplication

/ Division

\*\* Exponentiation

MOD Modulus

REM Remainder

ABS Absolute value

#### Addition example

| Name 🛆              | Value | S |     | 1 | 2    | ı    |  |

|---------------------|-------|---|-----|---|------|------|--|

| ±π <sub>9</sub>     | 08    |   | (08 |   |      |      |  |

| + т Р               | 02    | Ì | (02 |   |      |      |  |

| – π χ               | QA    |   | (0A |   |      |      |  |

| лг <sub>X</sub> (7) | 0     |   |     |   |      |      |  |

| лг x(6)             | 0     |   |     |   |      |      |  |

| лг <sub>X</sub> (5) | 0     |   |     |   |      |      |  |

| лг <sub>X</sub> (4) | 0     |   |     |   |      |      |  |

| лг X(3)             | 1     | Ì |     |   | <br> | <br> |  |

| лг x(2)             | 0     | Ì |     |   | <br> | <br> |  |

| лг <sub>X</sub> (1) | 1     |   |     |   | <br> | <br> |  |

| ът ×(0)             | 0     | Ì |     |   | <br> | <br> |  |

|                     |       |   |     |   | <br> | <br> |  |

```

LIBRARY ieee;

use ieee.std_logic_1164.all;

-- extra package necessary

use ieee.std_logic_arith.all;

entity test is

end entity;

architecture myarch of test is

signal a: signed (7 downto 0);

signal b: signed (7 downto 0);

signal x: signed (7 downto 0);

begin

a <= x"08"; --hexadecimal

--a \le "000001000"; --same as above

b \le x"02";

x \le a + b;

end architecture;

```

#### Subtraction example

| Name 🛆              | Value | S        | 1 . 2 . 1 . 4 . |

|---------------------|-------|----------|-----------------|

| .πa                 | 08    |          | (08             |

| <del></del> Р       | 02    |          | (02             |

| Εmγ                 | 06    |          | (06             |

| <b>nr</b> x(7)      | 0     |          |                 |

| <b>™</b> x(6)       | 0     |          |                 |

| лг x(5)             | 0     |          |                 |

| лг <sub>X</sub> (4) | 0     |          |                 |

| ът X(3)             | 0     |          |                 |

| лг <sub>X</sub> (2) | 1     |          |                 |

| лг <sub>X</sub> (1) | 1     |          |                 |

| ът X(0)             | 0     | <u></u>  |                 |

|                     |       | <b>^</b> |                 |

```

LIBRARY ieee;

use ieee.std_logic_1164.all;

-- extra package necessary

use ieee.std_logic_arith.all;

entity test is

end entity;

architecture myarch of test is

signal a: signed (7 downto 0);

signal b: signed (7 downto 0);

signal x: signed (7 downto 0);

begin

a <= x"08"; --hexadecimal

--a \le "000001000"; --same as above

b \le x"02";

x \le a - b;

end architecture;

```

#### Multiplication example

| Name 🛆               | Value | S | - 1  | 1443 ps |

|----------------------|-------|---|------|---------|

| т и a                | 08    |   | (08  | 1110 ps |

| <b>+ n.</b> P        | 02    |   | (02  |         |

| <u> п</u> х          | 0010  |   | 0010 |         |

| м <sub>X</sub> (15)  | 0     |   |      |         |

| лг х(14)             | 0     |   |      |         |

| <b>лг</b> х(13)      | 0     |   |      |         |

| <b>лг</b> х(12)      | 0     |   |      |         |

| м <sub>X</sub> (11)  | 0     |   |      |         |

| лг <sub>X</sub> (10) | 0     |   |      |         |

| лг X(მ)              | 0     |   |      |         |

| лг x(8)              | 0     |   |      |         |

| лг <sub>х</sub> (7)  | 0     |   |      |         |

| лг x(6)              | 0     |   |      |         |

| лг x(5)              | 0     |   |      |         |

| лг x(4)              | 1     |   |      |         |

| <b>л</b> г Х(3)      | 0     |   |      |         |

| <b>л</b> г х(2)      | 0     |   |      |         |

| лг <sub>X</sub> (1)  | 0     |   |      |         |

| м x(0)               | 0     |   |      |         |

|                      |       |   |      |         |

```

LIBRARY ieee;

use ieee.std_logic_1164.all;

-- extra package necessary

use ieee.std_logic_arith.all;

entity test is

end entity;

architecture myarch of test is

signal a: signed (7 downto 0);

signal b: signed (7 downto 0);

signal x: signed (15 downto 0);

begin

a <= x"08"; --hexadecimal

--a \le "000001000"; --same as above

b \le x"02";

x \le a * b;

end architecture;

```

#### This is WRONG!

- With signed data-types I can ONLY perform arithmetic operations

- This means, no logic operations

- I need to do something else to make this work.

```

LIBRARY ieee;

use ieee.std_logic_1164.all;

-- extra package necessary

use ieee.std_logic_arith.all;

entity test is

end entity;

architecture myarch of test is

signal a: signed (7 downto 0);

signal b: signed (7 downto 0);

signal x: signed (7 downto 0);

begin

a <= x"08"; --hexadecimal

--a \le "000001000"; --same as above

b \le x"02";

x \le a AND b;

end architecture;

```

#### More arithmetic

#### Arithmetic with integers

| Name A | Value | S |     | ī | 2,0 | ı |

|--------|-------|---|-----|---|-----|---|

| мa     | 10    |   | (10 |   |     |   |

| wР     | 11    |   | (11 |   |     |   |

| лг X   | 21    |   | (21 |   |     |   |

|        |       |   |     |   |     |   |

- You can do arithmetic with integers

- You CAN'T do logic operations with integers

```

LIBRARY ieee;

use ieee.std_logic_1164.all;

-- extra package necessary

use ieee.std logic arith.all;

entity test is

end entity;

architecture myarch of test is

signal a : integer := 10;

signal b : integer := 11;

signal x : integer;

begin

x \le a + b;

end architecture;

```

# Arithmetic with STD\_LOGIC\_VECTOR

| -               |    |     |

|-----------------|----|-----|

| ⊕ w a           | 01 | (01 |

| <b>∓ и</b> Р    | 03 | (03 |

| + nr X          | 04 | (04 |

| ⊟ ar y          | 01 | (01 |

| <b>n</b> r y(7) | 0  |     |

| <b>™</b> y(6)   | 0  |     |

| <b>™</b> y(5)   | 0  |     |

| ™ y(4)          | 0  |     |

| <b>n</b> r y(3) | 0  |     |

| <b>nr</b> y(2)  | 0  |     |

| <b>™</b> y(1)   | 0  |     |

| <b>ν</b> γ(0)   | 1  |     |

- You can still do logic!

- You can do arithmetic with STD\_LOGIC\_VECTOR but you must add and extra library:

```

- USE ieee.std logic unsigned.all;

```

```

LIBRARY ieee;

USE ieee.std logic 1164.all;

-- extra package included

USE ieee.std_logic_unsigned.all;

entity test is

end entity;

architecture myarch of test is

SIGNAL a: STD LOGIC VECTOR (7 DOWNTO 0);

SIGNAL b: STD LOGIC VECTOR (7 DOWNTO 0);

SIGNAL x: STD LOGIC VECTOR (7 DOWNTO 0);

SIGNAL y: STD LOGIC VECTOR (7 DOWNTO 0);

begin

a <= "0000001";

b <= "0000011";

x \le a + b;

y \le a AND b;

```

end architecture;

CPE 462 - VHDL: Simulation and Synthesis - Fall 'I I Nuno Alves (nalves@wne.edu), College of Engineering

#### Data conversion

#### Converting between data-types

- VHDL does not allow direct operations (arithmetic, logical, etc.)

between data of different types

- However, it is often necessary to convert data from one type to another

- There are special functions that allow us to convert from one type to another

- I can convert from certain data-types into

- integers

- signed / unsigned

- std\_logic\_vector

#### conv\_integer(p)

conv\_integer(p) : Converts a

parameter p of type UNSIGNED,

SIGNED, or STD\_ULOGIC to an

INTEGER value

```

LIBRARY ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_arith.all;

entity test is

end entity;

architecture myarch of test is

signal a: signed (7 downto 0);

signal x: integer;

begin

a <= "00000011";

x <= conv_integer (a);

end architecture;</pre>

```

### conv\_unsigned(p, b)

#### conv\_unsigned(p, b) :

Converts a parameter p of type INTEGER, UNSIGNED, SIGNED, or STD\_ULOGIC to an UNSIGNED value with size b bits.

```

LIBRARY ieee;

use ieee.std_logic_1164.all;

-- extra package necessary

use ieee.std logic arith.all;

entity test is

end entity;

architecture myarch of test is

signal a : integer;

signal x: unsigned (7 downto 0);

begin

a <= 10;

x <= conv_unsigned (a,8);</pre>

end architecture;

```

### conv\_signed(p, b)

conv\_signed(p, b): Converts a parameter p of type INTEGER, UNSIGNED, SIGNED, or STD\_ULOGIC to a SIGNED value with size b bits

```

LIBRARY ieee;

use ieee.std logic 1164.all;

-- extra package necessary

use ieee.std logic arith.all;

entity test is

end entity;

architecture myarch of test is

signal a : integer;

signal x: signed (7 downto 0);

begin

a <= 10;

x <= conv_signed (a,8);</pre>

end architecture;

```

## conv\_std\_logic\_vector(p, b)

#### conv\_std\_logic\_vector(p, b):

Converts a parameter p of type INTEGER, UN- SIGNED, SIGNED, or STD\_LOGIC to a STD\_LOGIC\_VECTOR value with size b bits.

```

LIBRARY ieee;

use ieee.std_logic_1164.all;

-- extra package necessary

use ieee.std logic arith.all;

entity test is

end entity;

architecture myarch of test is

signal a : integer;

signal x: std logic vector (7 downto

0);

begin

a <= 10;

x <= conv std logic vector (a,8);

end architecture;

```

# Summary

### Important to remember!

- You can only perform arithmetic operations with signed/ unsigned, integers and std\_logic\_vector types (with extra libraries)

- You can only perform logic operations with std\_logic (or closely related types)

- You can use certain functions to convert from one data-type into another

### Arithmetic and logic operations

- You can only perform arithmetic <u>and</u> logic operations with std\_logic\_vector types.

- Make sure you add all the following libraries:

```

library ieee;

use ieee.std_logic_I 164.all;

use ieee.std_logic_unsigned.all;

use ieee.std_logic_arith.all;

```

```

library ieee;

What is the difference between

use ieee.std logic 1164.all;

these two codes?

entity test is

end entity;

architecture myarch of test is

type matrix is array (2 downto 0) of std_logic_vector(4 downto 0);

signal x: matrix := ( "01000", "10010", "11001");

Values are assigned

begin

only at the beginning

end architecture;

library ieee;

use ieee.std logic 1164.all;

entity test is

end entity;

architecture myarch of test is

type matrix is array (2 downto 0) of std logic vector(4 downto 0);

signal x: matrix;

begin

Values are constantly

x(0) \le "11001";

being assigned (and in

x(1) \le "10010";

x(2) \le "01000";

parallel)!

```

(time=0)!

end architecture;

### Why is this illegal?

```

library ieee;

use ieee.std_logic_1164.all;

entity test is

port (signal x: in bit);

end entity;

architecture myarch of test is

begin

x <= '0';

end architecture;</pre>

```

#### **Extremely important!**

I can't assign values to the circuit inputs!

### Practice Exercises

### Exercise #1 - Arithmetic

- Create a circuit in VHDL that has in 3 inputs (**a**, **b** and **op**) and a single output (**output**). You may add a **CLK** signal if you want.

- a, b and op are 2 bit-buses of type std\_logic\_vector

- output is of type integer

- If op has the value "10" then add a and b and send the results to output

- If **op** has the value "01" then subtract **a** from **b** and send the results to **output**

- For any other op value, output should be 0

- Test your work with a test-bench!

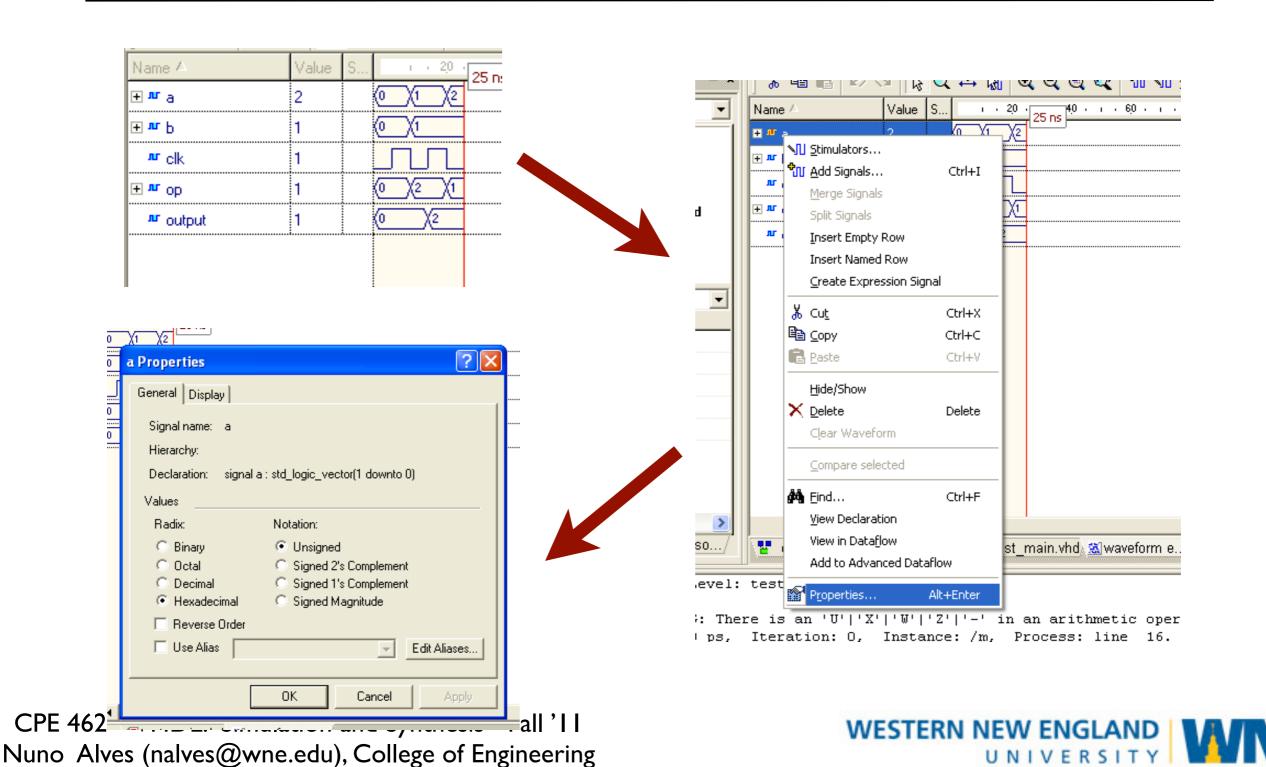

## Warnings on exercise #1

- While we have studied **processes**, you

have seen them in homework assignments

and its easier to get things done with them.

- Inside **processes** everything is done sequentially, that means your output will probably not be displayed exactly when your stimulus is triggered.

- Bottom line... you may want to add a clock to make things easier

```

entity exercise1 is

port (a,b,op : in std_logic_vector(1 downto 0);

clk : in bit;

output : out integer

);

```

| Name A       | Value | S | 1 · 20 · 25 n:                               |

|--------------|-------|---|----------------------------------------------|

| ±ма          | 2     |   | 0 X1 X2                                      |

| <b>± n</b> P | 1     |   | <u>0                                    </u> |

| лг clk       | 1     |   |                                              |

| <b>.π</b> ορ | 1     |   | 0 X2 X1                                      |

| ™ output     | 1     |   | 0 (2                                         |

|              |       |   |                                              |

|              |       |   |                                              |

## Exercise #2 - Why legal?

- Look at the following assignments.

- Why are they legal?

```

x(0) \le y(1)(2);

TYPE row IS ARRAY (7 DOWNTO 0) OF STD LOGIC;

-- 1D array

x(1) \le v(2)(3);

TYPE arrayl IS ARRAY (0 TO 3) OF row;

x(2) \le w(2,1);

-- 1Dx1D array

y(1)(1) \le x(6);

TYPE array2 IS ARRAY (0 TO 3) OF STD_LOGIC_VECTOR(7 DOWNTO 0);

y(2)(0) \le v(0)(0);

-- 1Dx1D

where,

y(0)(0) \le w(3,3);

TYPE array3 IS ARRAY (0 TO 3, 7 DOWNTO 0) OF STD LOGIC;

w(1,1) \le x(7);

-- 2D array

w(3,0) \le v(0)(3);

SIGNAL x: row;

y(1)(7 DOWNTO 3) \le x(4 DOWNTO 0);

SIGNAL y: array1;

SIGNAL v: array2;

v(1)(7 DOWNTO 3) \le v(2)(4 DOWNTO 0);

SIGNAL w: array3;

y(1)(7 DOWNTO 3) \le x(4 DOWNTO 0);

v(1)(7 DOWNTO 3) \le v(2)(4 DOWNTO 0);

```

## Exercise #3 - Why illegal?

- Look at the following assignments.

- Why are they illegal?

```

TYPE row IS ARRAY (7 DOWNTO 0) OF STD LOGIC;

-- 1D array

x \le v(1);

TYPE arrayl IS ARRAY (0 TO 3) OF row;

-- 1Dx1D array

x \le w(2);

TYPE array2 IS ARRAY (0 TO 3) OF STD LOGIC VECTOR(7 DOWNTO 0);

x \le w(2, 2 DOWNTO 0);

-- 1Dx1D

where,

TYPE array3 IS ARRAY (0 TO 3, 7 DOWNTO 0) OF STD LOGIC;

v(0) \le w(2, 2 DOWNTO 0);

-- 2D array

SIGNAL x: row;

v(0) \le w(2);

SIGNAL y: array1;

y(1) \le v(3);

SIGNAL v: array2;

w(1, 5 DOWNTO 1) \le v(2)(4 DOWNTO 0);

SIGNAL w: array3;

```

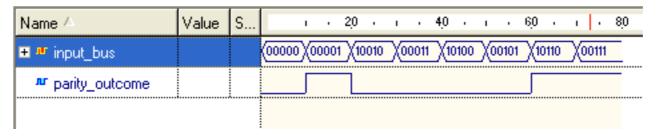

### Exercise #4 - Parity encoder

- A parity bit is a bit that is added to ensure that the number of bits with the value "one" in a set of bits is even or odd

- Parity bits are used as the simplest form of error detecting code

- If the number of "ones" is even the parity bit will be 0

- I challenge you to write a program that will find the parity bit for a 4-bit bus of type std\_logic\_vector

- Use the test-bench on the course website and the following entity:

```

entity parity_encoder is

port (input_bus : in std_logic_vector(3 downto 0);

output_bus : out std_logic_vector(4 downto 0)

);

end entity;

```

## Exercise #5 - Parity decoder

- Create another VHDL program that will tell if the parity of a 4bit bus is correct or not.

- Use the test-bench on the course website and the following entity:

So you can check your answer, here is the output after 80ns