### CPE 462 VHDL: Simulation and Synthesis

Topic #05 - c) BLOCK statements

#### **BLOCK** statement

- The BLOCK statement, in its simple form, represents only a way of locally partitioning the code.

- It allows a set of concurrent statements to be clustered into a BLOCK, with the purpose of turning the overall code more readable and more manageable

```

label: BLOCK

[declarative part]

BEGIN

(concurrent statements)

END BLOCK label;

```

### "Blocked" code

Therefore, the overall aspect of a "blocked" code is the following:

```

ARCHITECTURE example ...

BEGIN

...

block1: BLOCK

BEGIN

...

bl: BLOCK

END BLOCK block1

...

block2: BLOCK

BEGIN

a <= input_sig WHEN ena='1' ELSE 'Z';

END BLOCK block2;

...

END BLOCK block2;

...

END example;

```

### Guarded BLOCK

- A guarded BLOCK is a special kind of BLOCK, which includes an additional expression, called guard expression.

- A guarded statement in a guarded BLOCK is executed only when the guard expression is TRUE.

- Note: Only concurrent statements can be written within a BLOCK. However, with a guarded BLOCK even sequential circuits can be constructed.

#### Guarded BLOCK:

```

label: BLOCK (guard expression)

[declarative part]

BEGIN

(concurrent guarded and unguarded statements)

END BLOCK label;

```

### Latch example with BLOCK

- The example presented implements a transparent latch.

- In it, clk='I' (line 12) is the guard expression, while q<=GUARDED d (line 14) is a guarded statement.

- Therefore, q<=d will only occur if clk='I'.

# DFF Implemented with a Guarded BLOCK

- Positive-edge sensitive D-type flipflop, with synchronous reset, is designed.

- The clk'EVENT AND clk='I' (line I2) is the guard expression, while q

GUARDED '0' WHEN rst='I' (line I4) is a guarded statement.

- Therefore, q<='0' will occur when the guard expression is true and rst is '1'.

```

2 LIBRARY ieee;

USE ieee.std_logic_1164.all;

ENTITY dff IS

PORT ( d, clk, rst: IN STD LOGIC;

q: OUT STD_LOGIC);

END dff;

10 ARCHITECTURE dff OF dff IS

11 BEGIN

b1: BLOCK (clk'EVENT AND clk='1')

BEGIN

14

q <= GUARDED '0' WHEN rst='1' ELSE d;</pre>

15

END BLOCK b1;

16 END dff;

```

### Small (but fundamental) detour

## Variable Scope in C

```

float valA=12.5; float valB=16.1;

void print variable scope()

int intVariable=10;

Serial.println(intVariable);

Serial.println(valA); //valA is global

//ERROR! Variable res is out of Scope

Serial.println(res);

void loop()

print variable scope();

float res = 12.5;

Serial.println(res);

//ERROR! intVariable is out of Scope

Serial.println(intVariable);

```

- The scope of a variable is where it can be used in a program

- Normally variables are local in scope

this means they can only be used in the function where they are declared (main is a function)

- We can also declare global variables.

- If we declare a variable outside a function it can be used in any function beneath where it is declared

- Global variables are A BAD THING...

Try to minimize their use.

WESTERN NEW ENGLAND

UNIVERSITY

- Signal a is only active inside block b l

- In the declaration part of "blocks", "processes" or "architectures" you can declare signals that are only active **INSIDE** that section of code

```

ARCHITECTURE architecture_name OF entity_name IS

[declarations]

BEGIN

(code)

END architecture_name;

```

```

entity test is

port (clk : in bit);

end entity:

architecture myarch of test is

signal b : bit;

begin

b1: block (clk='1')

signal a : bit;

10

begin

b<='0';

12

a<='0':

13

end block:

14

15

end architecture:

16

17

```

- This is not OK!

- The signal a is not available outside the block b1

```

entity test is

port (clk : in bit);

end entity:

architecture myarch of test is

signal b : bit;

begin

b1: block (clk='1')

signal a : bit;

10

begin

b<='0';

12

end block:

13

14

a<='0';

15

end architecture;

16

```

This is the scope of signal b

```

entity test is

port (clk : in bit);

end entity:

architecture myarch of test is

signal b : bit;

begin

b1: block (clk='1')

signal a : bit;

10

begin

b<='0';

12

a<='0';

13

end block:

14

15

end architecture;

```

• This is the scope of signal a

```

entity test is

port (clk : in bit);

end entity:

architecture myarch of test is

signal b : bit;

begin

b1: block (clk='1')

signal a : bit;

10

begin

b<='0';

12

a<='0';

13

end block:

14

15

end architecture;

16

```

### Practice Exercises

### Comparator

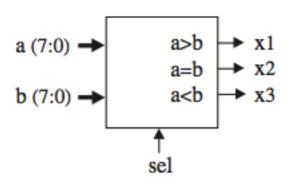

Construct a circuit capable of comparing two 8-bit vectors, a and b. A selection pin (sel) should determine whether the comparison is signed (sel = '1') or unsigned (sel='0'). The circuit must have three outputs,  $x \mid x^2$ , and  $x^3$ , corresponding to a > b, a=b, and a < b, respectively.