## CPE 462 VHDL: Simulation and Synthesis

Topic #06 - a) PROCESS, If and Variables

### Mini-Review

- Last week we discussed concurrentcode.

- Concurrent-code is also known as dataflow-code.

- What is concurrent code?

- We will now talk about sequential code.

- Sequential-code is also know as behavioral code.

```

entity main block is

port (clk, a, b : in bit);

end main block;

architecture myarch of main_block is

signal x,y,z : bit;

begin

x \le a AND b;

y \le a XOR b;

process (clk)

begin

y \le a OR b;

end process

end architecture;

```

### Sequential Code

- VHDL code is inherently concurrent.

- PROCESSES, FUNCTIONS, and PROCEDURES are the only sections of code that are executed sequentially.

- However, as a whole, any of these blocks is still concurrent with any other statements placed outside it.

- With sequential code we can build sequential circuits as well as combinational circuits.

```

entity main block is

port (clk, a, b : in bit);

end main block;

architecture myarch of main_block is

signal x,y,z : bit;

begin

x \le a AND b;

y \le a XOR b;

process (clk)

begin

y \le a OR b;

end process

end architecture;

```

CPE 462 - VHDL: Simulation and Synthesis - Fall 'I I Nuno Alves (nalves@wne.edu), College of Engineering

- The following statements are only valid inside sequential code (such as processes): IF, WAIT, CASE, and LOOP.

- **Warning:** The following statements are only valid inside concurrent code: WHEN, GENERATE, BLOCK.

- VARIABLES are also restricted to be used in sequential code only (for example, inside a PROCESS).

- Contrary to a SIGNAL, a VARIABLE can never be global, so its value can not be passed out directly.

- We will talk about VARIABLES today.

### **PROCESS**

- A PROCESS is a sequential section of VHDL code.

- It is characterized by the presence of IF, WAIT, CASE, or LOOP, and by a sensitivity list (except when WAIT is used).

What is a sensitivity list?

- Its a list of signals in parenthesis, which tells when the process should be re-evaluated to update the outputs.

- The signal sensitivity list is used to specify which signals should cause the process to be re-evaluated.

```

CPE 462 - VHDL: Simulation and Synthesis - Fall 'I I Nuno Alves (nalves@wne.edu), College of Engineering

```

```

entity main block is

port (clk, a, b : in bit);

end main block;

architecture myarch of main block is

signal x,y,z : bit;

begin

x \le a AND b;

y \le a XOR b;

process (clk)

begin

y \le a OR b;

end process

end architecture;

```

### **PROCESS**

- A PROCESS must be installed in the main code, and is executed every time a signal in the sensitivity list changes (or the condition related to WAIT is fulfilled).

- Its syntax is shown below:

```

[label:] PROCESS (sensitivity list)

[VARIABLE name type [range] [:= initial_value;]]

BEGIN

(sequential code)

END PROCESS [label];

```

```

entity main block is

port (clk, a, b : in bit);

end main_block;

architecture myarch of main block is

signal x,y,z : bit;

begin

x \le a AND b;

y \le a XOR b;

process (clk)

begin

y \le a OR b;

end process

end architecture;

```

CPE 462 - VHDL: Simulation and Synthesis - Fall 'I I Nuno Alves (nalves@wne.edu), College of Engineering

### **PROCESS**

```

[label:] PROCESS (sensitivity list)

[VARIABLE name type [range] [:= initial_value;]]

BEGIN

(sequential code)

END PROCESS [label];

```

- VARIABLES are optional.

- If variables are used, they must be declared in the declarative part of the PROCESS (before the word BEGIN).

- The initial value is not synthesizable, being only taken into consideration in simulations.

- The use of a label is also optional. Its purpose is to improve code readability.

```

CPE 462 - VHDL: Simulation and Synthesis - Fall 'I I Nuno Alves (nalves@wne.edu), College of Engineering

```

```

entity main block is

port (clk, a, b : in bit);

end main block;

architecture myarch of main block is

signal x,y,z : bit;

begin

x \le a AND b;

y \le a XOR b;

process (clk)

begin

y \le a OR b;

end process

end architecture;

```

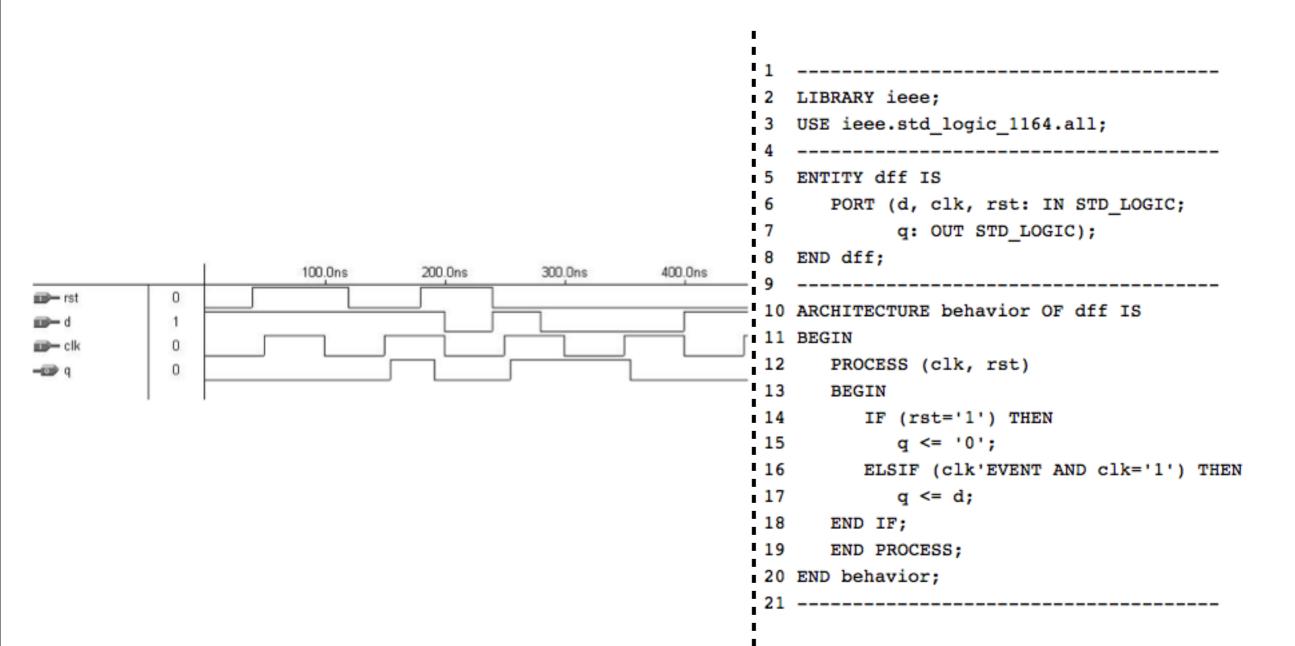

## Constructing a synchronous circuit

- To construct a synchronous circuit, monitoring a signal (clock, for example) is necessary.

- A common way of detecting a signal change is by means of the EVENT data-attribute.

- For instance, if clk is a signal to be monitored, then clk'EVENT returns TRUE when a change on clk occurs (rising or falling edge).

```

DFF

USE ieee.std_logic_1164.all;

PORT (d, clk, rst: IN STD LOGIC;

q: OUT STD LOGIC);

0 ARCHITECTURE behavior OF dff IS

PROCESS (clk, rst)

IF (rst='1') THEN

ELSIF (clk'EVENT AND clk='1') THEN

END IF;

END PROCESS;

END behavior:

```

### Constructing a synchronous circuit

- A D-type flip-flop (DFF) is the most basic building block in sequential logic circuits. In it, the output must copy the input at either the positive or negative transition of the clock signal (rising or falling edge).

- Here we use the IF statement (to be discussed later) to design a DFF with asynchronous reset. If rst='1', then the output must be q='0' (lines 14–15), regardless of the status of clk.

```

DFF

LIBRARY ieee;

USE ieee.std_logic_1164.all;

PORT (d, clk, rst: IN STD_LOGIC;

q: OUT STD LOGIC);

0 ARCHITECTURE behavior OF dff IS

PROCESS (clk, rst)

IF (rst='1') THEN

15

16

ELSIF (clk'EVENT AND clk='1') THEN

17

END IF;

END PROCESS;

END behavior;

```

### Constructing a synchronous circuit

### Introduction to signals and variables

- VHDL has two ways of passing nonstatic values around: SIGNAL or by a VARIABLE.

- A SIGNAL can be declared in the declarative part of the architecture (or inside a block), while a VARIABLE can only be declared inside a piece of sequential code. Therefore, a signal can be be global, a variable is always local.

- What is the scope of a, b and c?

```

entity test is

port (clk : in bit);

end entity;

architecture myarch of test is

signal b : bit;

begin

'b1: block

signal a : bit;

begin

a<='0';

!end block;

process (clk)

variable c : bit;

begin

b<='0';

end process;

end architecture;

```

## Declaring signals inside processes is not OK

- VHDL has two ways of passing nonstatic values around: SIGNAL or by a VARIABLE.

- A SIGNAL can be declared in the declarative part of the architecture (or inside a block), while a VARIABLE can only be declared inside a piece of sequential code. Therefore, a signal can be be global, a variable is always local.

- What is the scope of a, b and c?

```

entity test is

port (clk : in bit);

end entity:

architecture myarch of test is

signal b : bit;

begin

b1: block

signal a : bit;

10

begin

11

a<='0';

12

end block:

13

14

process (clk)

15

signal c : bit;

16

begin

b<='0';

17

18

end process;

19

end architecture;

```

# Declaring variables outside processes is not OK

- VHDL has two ways of passing nonstatic values around: SIGNAL or by a VARIABLE.

- A SIGNAL can be declared in the declarative part of the architecture (or inside a block), while a VARIABLE can only be declared inside a piece of sequential code. Therefore, a signal can be be global, a variable is always local.

- What is the scope of a, b and c?

```

entity test is

port (clk : in bit);

end entity:

architecture myarch of test is

variable b : bit;

begin

b1: block

signal a : bit;

10

begin

11

a<='0';

12

end block:

13

14

process (clk)

15

variable c : bit:

16

begin

17

b<= '0';

18

end process;

19

20

end architecture:

```

### More on variables

- The value of a VARIABLE can never be passed out of the PROCESS directly; if necessary, then it must be assigned to a SIGNAL.

- On the other hand, the update of a VARIABLE is immediate, that is, we can promptly count on its new value in the next line of code.

- That is not the case with a SIGNAL (when used in a PROCESS), for its new value is generally only guaranteed to be available after the conclusion of the present run of the PROCESS.

### Signal update inside a PROCESS

end architecture;

- A SIGNAL (when used in a PROCESS), is generally only guaranteed to be available after the conclusion of the present run of the PROCESS.

- Seriously? So what should x waveform be?

```

library ieee;

use ieee.std logic 1164.all;

use ieee.std logic unsigned.all;

entity test is

port (clk : in bit);

end entity;

architecture myarch of test is

signal x : std logic vector(3 downto 0):="0000";

begin

process (clk)

begin

x <= x+1;

x <= x+1;

end process;

```

CPE 462 - VHDL: Simulation and Synthesis - Fall 'I' Nuno Alves (nalves@wne.edu), College of Engineering

### Signal update inside a PROCESS

- A SIGNAL (when used in a PROCESS), is generally only guaranteed to be available after the conclusion of the present run of the PROCESS.

- Seriously? So what should x waveform be?

| Name 🛆       | Value | S |   | , | 5    | ,    | 10   | ,    | 15   |  |

|--------------|-------|---|---|---|------|------|------|------|------|--|

| <b>P</b> clk | 0     | C |   |   |      |      | l    | <br> |      |  |

| ± w X        | 11    |   | Œ |   | X2   |      | X3   |      | X4   |  |

|              |       |   |   |   | <br> | <br> | <br> | <br> | <br> |  |

CPE 462 - VHDL: Simulation and Synthesis - Fall 'I' Nuno Alves (nalves@wne.edu), College of Engineering

```

library ieee;

use ieee.std logic 1164.all;

use ieee.std logic unsigned.all;

entity test is

port (clk : in bit);

end entity;

architecture myarch of test is

signal x : std logic vector(3 downto 0):="0000";

begin

process (clk)

begin

x <= x+1;

x <= x+1;

end process;

end architecture;

```

## Assignment operator

- The assignment operator for a SIGNAL is "<="

- The assignment operator for a VARIABLE it is ":="

```

library ieee;

use ieee.std logic 1164.all;

use ieee.std logic unsigned.all;

entity test is

port (clk : in bit);

end entity:

architecture myarch of test is

signal x : std logic vector(3 downto 0):="0000";

11

begin

12

13

process (clk)

variable c : std logic vector(3 downto 0);

begin

x \le x+1;

c := c+1;

end process;

19

20

end architecture;

```

### IF statement

- As mentioned earlier, IF, WAIT, CASE, and LOOP are the statements intended for sequential code.

- Therefore, they can only be used inside a PROCESS, FUNCTION, or PROCEDURE.

```

IF conditions THEN assignments;

ELSIF conditions THEN assignments;

...

ELSE assignments;

END IF;

```

#### Example:

```

IF (x<y) THEN temp:="111111111";

ELSIF (x=y AND w='0') THEN temp:="11110000";

ELSE temp:=(OTHERS =>'0');

```

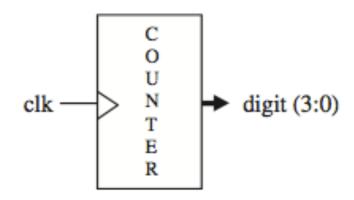

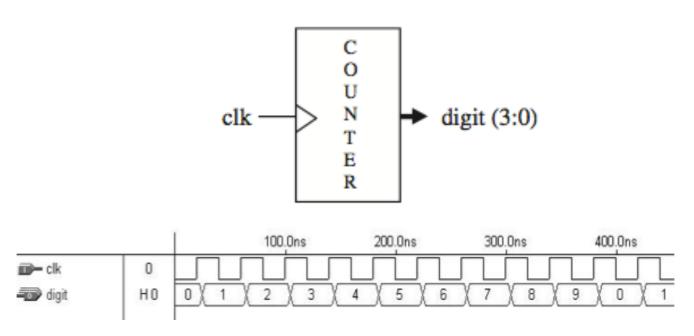

## Example: One-digit Counter

This code implements a progressive I-digit decimal counter (0 to 9 to 0).

It contains a single input (clk) and a 4-bit output (digit). The IF statement is used in this example. A variable, temp, was employed to create the four flip-flops necessary to store the 4-bit output signal.

```

LIBRARY ieee;

USE ieee.std_logic_1164.all;

ENTITY counter IS

PORT (clk : IN STD LOGIC;

digit : OUT INTEGER RANGE 0 TO 9);

END counter;

10 ARCHITECTURE counter OF counter IS

11 BEGIN

12

count: PROCESS(clk)

13

VARIABLE temp : INTEGER RANGE 0 TO 10;

BEGIN

IF (clk'EVENT AND clk='1') THEN

temp := temp + 1;

16

IF (temp=10) THEN temp := 0;

17

18

END IF;

19

END IF;

20

digit <= temp;

END PROCESS count;

22 END counter;

```

## Example: One-digit Counter

Minor problems with this code:

- What is the initial value of temp?

- How can I initialize this circuit to start counting at zero?

```

LIBRARY ieee;

USE ieee.std_logic_1164.all;

ENTITY counter IS

PORT (clk : IN STD LOGIC;

digit : OUT INTEGER RANGE 0 TO 9);

END counter;

10 ARCHITECTURE counter OF counter IS

11 BEGIN

12

count: PROCESS(clk)

13

VARIABLE temp : INTEGER RANGE 0 TO 10;

14

BEGIN

IF (clk'EVENT AND clk='1') THEN

15

16

temp := temp + 1;

IF (temp=10) THEN temp := 0;

17

18

END IF;

19

END IF;

digit <= temp;

20

END PROCESS count;

22 END counter;

```