# CPE 462 VHDL: Simulation and Synthesis

Topic #06 - d) Final topics in sequential code

#### Loop example

- This design counts the number of leading zeros in a binary vector, starting from the left end.

- EXIT implies not a escape from the current iteration of the loop, but rather a definite exit from it (that is, even if i is still within the specified range, the LOOP statement will be considered as concluded).

- In this example, the loop will end as soon as a '1' is found in the data vector.

- Therefore, it is appropriate for counting the 22 ZETOS < 1 DEND PROCESS Number of zeros that precedes the first one 24 END behavior;

```

LIBRARY ieee;

USE ieee.std_logic_1164.all;

ENTITY LeadingZeros IS

PORT ( data: IN STD LOGIC VECTOR (7 DOWNTO 0);

zeros: OUT INTEGER RANGE 0 TO 8);

END LeadingZeros;

10 ARCHITECTURE behavior OF LeadingZeros IS

11 BEGIN

12

PROCESS (data)

VARIABLE count: INTEGER RANGE 0 TO 8;

BEGIN

count := 0;

FOR i IN data RANGE LOOP

CASE data(i) IS

WHEN '0' => count := count + 1;

WHEN OTHERS => EXIT;

20

END CASE;

21

END LOOP;

zeros <= count;

END PROCESS;

```

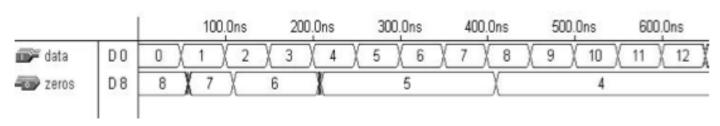

#### Loop example: simulation

With data="00000000" (decimal 0), eight zeros are detected; when data="00000001" (decimal 1), seven zeros are encountered; etc

```

2 LIBRARY ieee;

USE ieee.std_logic_1164.all;

ENTITY LeadingZeros IS

PORT ( data: IN STD LOGIC VECTOR (7 DOWNTO 0);

zeros: OUT INTEGER RANGE 0 TO 8);

END LeadingZeros;

ARCHITECTURE behavior OF LeadingZeros IS

11 BEGIN

PROCESS (data)

13

VARIABLE count: INTEGER RANGE 0 TO 8:

14

BEGIN

count := 0;

FOR i IN data'RANGE LOOP

CASE data(i) IS

17

18

WHEN '0' => count := count + 1;

WHEN OTHERS => EXIT:

END CASE;

21

END LOOP;

22

zeros <= count;

END PROCESS;

24 END behavior;

```

#### Bad Clocking

- The compiler will generally not be able to synthesize codes that contain assignments to the same signal at both transitions of the reference (clock) signal (that is, at the rising edge plus at the falling edge).

- This is particularly true when the target technology contains only single-edge flip-flops.

- As an example, let us consider the case of a counter that must be incremented at every clock transition (rising plus falling edge).

#### Bad Clocking Example #1

• The compiler will generally not be able to synthesize codes that contain assignments to the same signal at both transitions of the reference (clock) signal (that is, at the rising edge plus at the falling edge).

```

PROCESS (clk)

BEGIN

IF(clk'EVENT AND clk='1') THEN

counter <= counter + 1;

ELSIF(clk'EVENT AND clk='0') THEN

counter <= counter + 1;

END IF;

...

END PROCESS;

```

# Bad Clocking Example #2

- The compiler does not know if we are dealing with rising or falling edge.

- It may issue a message of the type "clock not locally stable"

- ... Or it may assume clk'event='0'.

- Don't do this!

```

PROCESS (clk)

BEGIN

IF(clk'EVENT) THEN

counter := counter + 1;

END IF;

...

END PROCESS;

```

# Good Clocking Example #1

If I want to perform an operation on both clk edges I need to declare two different processes

# Good Clocking Example #2: RAM

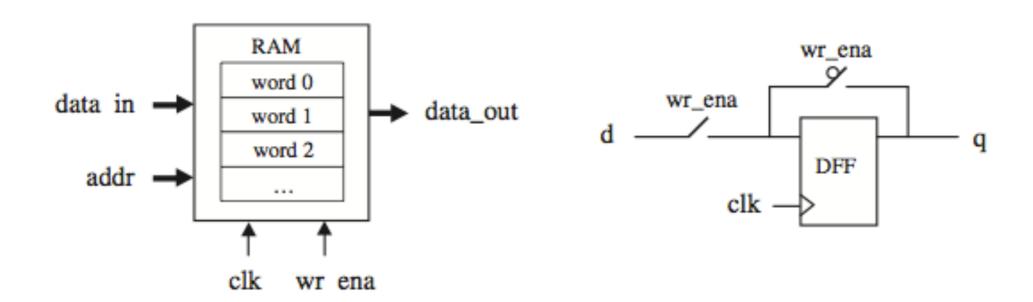

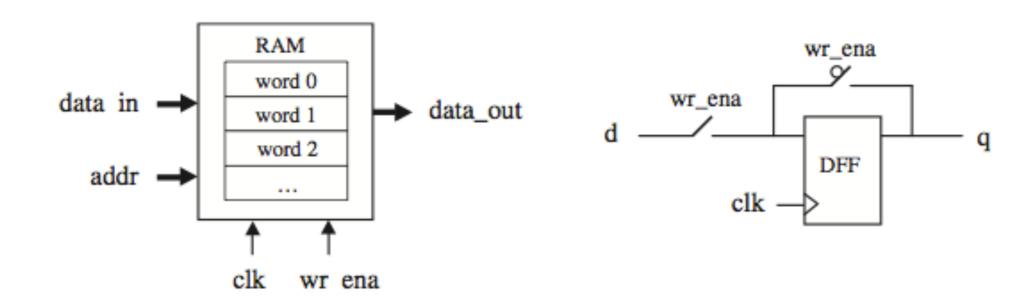

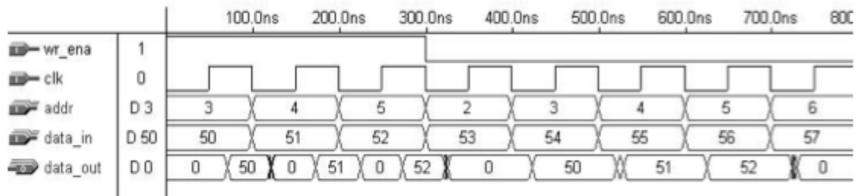

- The circuit has a data input bus (data\_in), a data output bus (data\_out), an address bus (addr), plus clock (clk) and write enable(wr\_ena) pins.

- When **wr\_ena** is asserted, at the next rising edge of **clk** the vector present at **data\_in** must be stored in the position specified by **addr**. The output, **data\_out**, on the other hand, must constantly display the data selected by **addr**.

# Good Clocking Example #2: RAM

- When **wr\_ena** is low, **q** is connected to the input of the flip-flop, and terminal **d** is open, so no new data will be written into the memory.

- However, when wr\_ena is turned high, d is connected to the input of the register, so at the next rising edge of clk, d will overwrite its previous value.

```

LIBRARY ieee;

USE ieee.std logic 1164.all;

ENTITY ram IS

GENERIC ( bits: INTEGER := 8; -- # of bits per word

words: INTEGER := 16); -- # of words in the memory

PORT ( wr ena, clk: IN STD LOGIC;

addr: IN INTEGER RANGE 0 TO words-1;

data in: IN STD LOGIC VECTOR (bits-1 DOWNTO 0);

data out: OUT STD LOGIC VECTOR (bits-1 DOWNTO 0));

12 END ram;

14 ARCHITECTURE ram OF ram IS

15

TYPE vector array IS ARRAY (0 TO words-1) OF

STD_LOGIC_VECTOR (bits-1 DOWNTO 0);

16

SIGNAL memory: vector array;

17

18 BEGIN

19

PROCESS (clk, wr ena)

20

BEGIN

IF (wr_ena='1') THEN

21

IF (clk'EVENT AND clk='1') THEN

23

memory(addr) <= data in;</pre>

24

END IF;

25

END IF;

26

END PROCESS;

data out <= memory(addr);</pre>

28 END ram;

```

- The capacity chosen for the RAM is 16 words of length 8 bits each.

- Notice that the code is totally generic.

CPE 462 - VHDL: Simulation and Synthesis - Fall 'I I Nuno Alves (nalves@wne.edu), College of Engineering