## CPE 462 VHDL: Simulation and Synthesis

Topic #07 - b) VHDL implementations

#### When to use a FSM

- Any sequential circuit can in principle be modeled as a state machine, this is not always advantageous.

- For example, implementing a counter as a FSM will likely result in longer, more complex, and more error prone than in a conventional approach.

- The FSM approach is advisable in systems whose tasks constitute a well-structured list so all states can be easily enumerated.

- For example digital controllers, such as traffic light and elevator controllers.

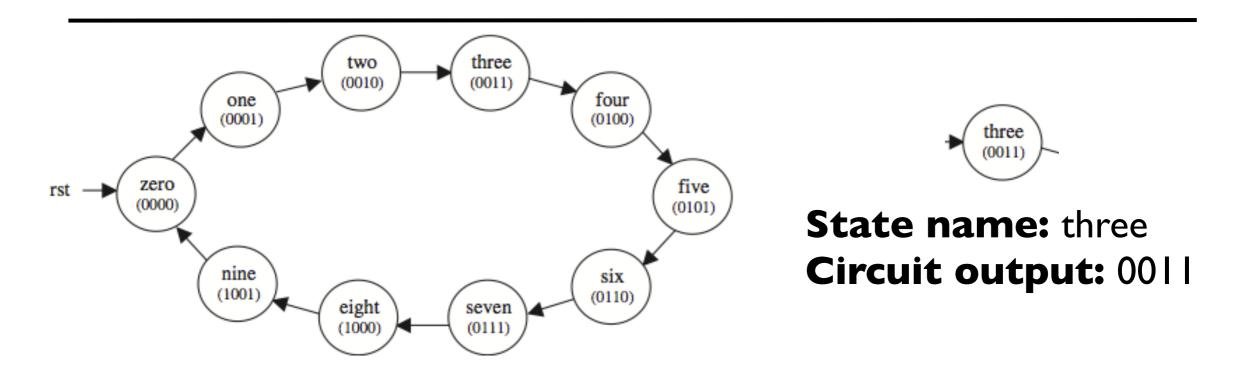

#### Example #1: BCD counter

two three (0010)(0011)• The state diagram of a 0-to-9 four one (0001)(0100)circular counter. five zero (00000)(0101) Each state-name corresponds to nine six the decimal value of the output. (1001)(0110)eight seven (1000)(01111)

- We could easily perform do this BCD counter using all that we learned thus far.

- However we are going to try to do this using a FSM, where each counter outcome is a particular state.

- As you can see, the output depends only on the current state.

#### Example #1: BCD counter

- The problem with a FSM implementation is that when the number of states is large it becomes cumbersome to enumerate them all.

- This is no problem if we were trying to count without using a FSM.

#### Example #1: BCD counter

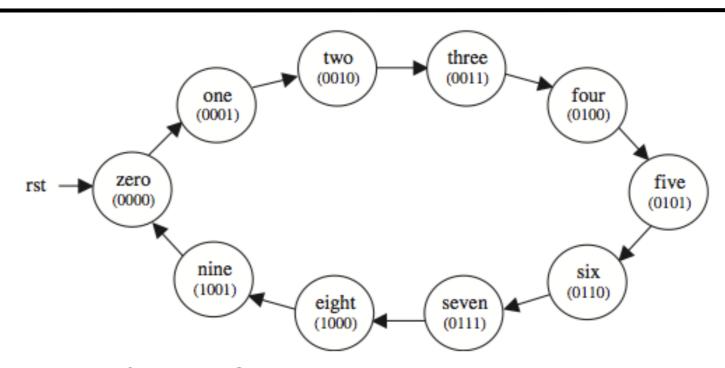

- The operation of this FSM is simple.

- At every rising-edge clock cycle it will change its state.

- When each state changes, the circuit will return a new output value.

- When **rst** is pressed, the present state will now be state zero.

```

four

LIBRARY ieee;

zero

USE ieee.std logic 1164.all;

(0101)

nine

ENTITY counter IS

(1001)

eight

(1000)

PORT ( clk, rst: IN STD LOGIC;

count: OUT STD LOGIC VECTOR (3 DOWNTO 0));

34

WHEN two =>

END counter;

35

count <= "0010";

36

nx state <= three;</pre>

10 ARCHITECTURE state_machine OF counter IS

TYPE state IS (zero, one, two, three, four,

37

WHEN three =>

11

38

count <= "0011";

12

five, six, seven, eight, nine);

39

nx state <= four;</pre>

SIGNAL pr_state, nx_state: state;

13

WHEN four =>

40

14 BEGIN

41

count <= "0100";

15

----- Lower section: ------

42

nx state <= five;</pre>

16

PROCESS (rst, clk)

43

WHEN five =>

17

BEGIN

18

44

count <= "0101";

IF (rst='1') THEN

45

nx state <= six;</pre>

19

pr state <= zero;

46

WHEN six =>

20

ELSIF (clk'EVENT AND clk='1') THEN

47

21

count <= "0110";

pr state <= nx state;</pre>

48

nx state <= seven;</pre>

22

END IF;

49

WHEN seven =>

23

END PROCESS;

50

count <= "0111";

24

----- Upper section: -----

25

51

nx state <= eight;</pre>

PROCESS (pr state)

52

WHEN eight =>

26

BEGIN

53

count <= "1000";

27

CASE pr_state IS

nx_state <= nine;</pre>

54

28

WHEN zero =>

55

WHEN nine =>

29

count <= "0000";

56

count <= "1001";

30

nx state <= one;</pre>

57

nx state <= zero;</pre>

31

WHEN one =>

58

END CASE;

32

count <= "0001";

59

END PROCESS;

33

nx state <= two;

60 END state machine;

```

CPE 462 - VHDL: Simulation and Synthesis - Fall 'I I Nuno Alves (nalves@wne.edu), College of Engineering

```

LIBRARY ieee;

USE ieee.std logic 1164.all;

ENTITY counter IS

PORT ( clk, rst: IN STD LOGIC;

count: OUT STD LOGIC VECTOR (3 DOWNTO 0));

END counter;

10 ARCHITECTURE state machine OF counter IS

TYPE state IS (zero, one, two, three, for

11

five, six, seven, eight, nine);

12

SIGNAL pr state, nx state: state;

13

14 BEGIN

15

----- Lower section: ------

16

PROCESS (rst, clk)

17

BEGIN

This is how you

18

IF (rst='1') THEN

pr_state <= zero;</pre>

use enumerated

19

ELSIF (clk'EVENT AND clk='1') THEN

20

data types.

21

pr_state <= nx_state;</pre>

22

END IF;

23

END PROCESS;

24

----- Upper section: -----

25

PROCESS (pr state)

26

BEGIN

27

CASE pr state IS

28

WHEN zero =>

29

count <= "0000";

nx state <= one;</pre>

31

WHEN one =>

32

count <= "0001";

33

nx state <= two;

```

The **state** (enumerated data type) is defined, and used for the **pr\_state** (present state) and **nx\_state** (next state).

```

34

WHEN two =>

35

count <= "0010";

36

nx state <= three;</pre>

37

WHEN three =>

38

count <= "0011";

39

nx state <= four;

WHEN four =>

40

count <= "0100";

41

42

nx state <= five;</pre>

43

WHEN five =>

44

count <= "0101";

45

nx state <= six;</pre>

46

WHEN six =>

47

count <= "0110";

48

nx state <= seven;</pre>

49

WHEN seven =>

count <= "0111";

50

51

nx state <= eight;</pre>

52

WHEN eight =>

53

count <= "1000";

54

nx state <= nine;</pre>

WHEN nine =>

55

56

count <= "1001";

57

nx state <= zero;</pre>

58

END CASE;

END PROCESS;

60 END state machine;

```

```

LIBRARY ieee;

USE ieee.std logic 1164.all;

ENTITY counter IS

PORT ( clk, rst: IN STD_LOGIC;

count: OUT STD LOGIC VECTOR (3 DOWNTO 0));

END counter;

10 ARCHITECTURE state_machine OF counter IS

TYPE state IS (zero, one, two, three, four,

11

12

five, six, seven, eight, nine);

SIGNAL pr state, nx state: state;

13

14 BEGIN

15

----- Lower section: ------

16

PROCESS (rst, clk)

17

BEGIN

18

IF (rst='1') THEN

19

pr state <= zero;</pre>

20

ELSIF (clk'EVENT AND clk='1') THEN

21

pr state <= nx state;</pre>

22

END IF;

23

END PROCESS;

24

----- Upper section: -----

25

PROCESS (pr state)

26

BEGIN

27

CASE pr state IS

28

WHEN zero =>

29

count <= "0000";

30

nx state <= one;</pre>

31

WHEN one =>

32

count <= "0001";

33

nx state <= two;

```

The output **count** is the circuit output at each stage.

```

34

WHEN two =>

35

count <= "0010";

36

nx state <= three;</pre>

37

WHEN three =>

38

count <= "0011";

39

nx state <= four;

WHEN four =>

40

count <= "0100";

41

42

nx state <= five;</pre>

43

WHEN five =>

44

count <= "0101";

45

nx state <= six;</pre>

46

WHEN six =>

47

count <= "0110";

48

nx state <= seven;</pre>

49

WHEN seven =>

50

count <= "0111";

51

nx state <= eight;</pre>

52

WHEN eight =>

53

count <= "1000";

54

nx state <= nine;</pre>

WHEN nine =>

55

56

count <= "1001";

57

nx state <= zero;</pre>

58

END CASE;

59

END PROCESS;

60 END state machine;

```

CPE 462 - VHDL: Simulation and Synthesis - Fall 'I I Nuno Alves (nalves@wne.edu), College of Engineering

```

LIBRARY ieee;

USE ieee.std logic 1164.all;

ENTITY <entity name> IS

PORT ( input: IN <data type>;

reset, clock: IN STD LOGIC;

output: OUT <data type>);

END <entity name>;

ARCHITECTURE <arch name> OF <entity name> IS

TYPE state IS (state0, state1, state2, state3, ...);

SIGNAL pr state, nx state: state;

BEGIN

----- Lower section: -----

PROCESS (reset, clock)

BEGIN

IF (reset='1') THEN

pr state <= state0;</pre>

ELSIF (clock'EVENT AND clock='1') THEN

pr state <= nx state;</pre>

END IF;

END PROCESS;

----- Upper section:

PROCESS (input, pr state)

CASE pr state IS

WHEN state0 =>

IF (input = ...) THEN

output <= <value>;

nx state <= state1;

ELSE ...

END IF:

WHEN state1 =>

IF (input = ...) THEN

output <= <value>;

nx state <= state2;

ELSE ...

END IF;

WHEN state2 =>

IF (input = ...) THEN

output <= <value>;

nx state <= state3;</pre>

ELSE ...

END IF:

END CASE;

END PROCESS:

END <arch name>;

```

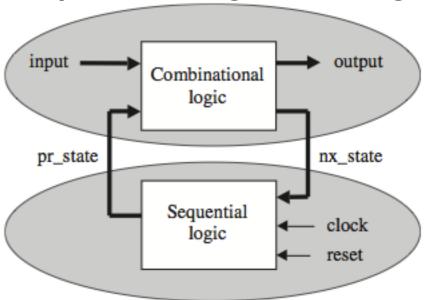

#### FSM template #1

Remember, in a FSM the next state depends on the current input and the current state.

- This template allows for the design of any FSM.

- The design of the lower section of the state machine is completely separated from that of the upper section.

```

LIBRARY ieee;

USE ieee.std logic 1164.all;

ENTITY <entity name> IS

PORT ( input: IN <data type>;

reset, clock: IN STD LOGIC;

output: OUT <data type>);

END <entity name>;

ARCHITECTURE <arch name> OF <entity name> IS

TYPE state IS (state0, state1, state2, state3, ...);

SIGNAL pr state, nx state: state;

BEGIN

----- Lower section: ------

PROCESS (reset, clock)

BEGIN

IF (reset='1') THEN

pr state <= state0;</pre>

ELSIF (clock'EVENT AND clock='1') THEN

pr state <= nx state;</pre>

END IF;

END PROCESS;

----- Upper section: -----

PROCESS (input, pr state)

CASE pr state IS

WHEN state0 =>

IF (input = ...) THEN

output <= <value>;

nx state <= state1;

ELSE ...

END IF:

WHEN state1 =>

IF (input = ...) THEN

output <= <value>;

nx state <= state2;

ELSE ...

END IF;

WHEN state2 =>

IF (input = ...) THEN

output <= <value>;

nx state <= state3;

ELSE ...

END IF:

END CASE;

END PROCESS:

END <arch name>;

```

#### FSM template #1

All states of the machine are always explicitly declared using an enumerated data type.

```

LIBRARY ieee;

USE ieee.std logic 1164.all;

ENTITY <entity name> IS

PORT ( input: IN <data type>;

reset, clock: IN STD LOGIC;

output: OUT <data type>);

END <entity name>;

ARCHITECTURE <arch name> OF <entity name> IS

TYPE state IS (state0, state1, state2, state3, ...);

SIGNAL pr state, nx state: state;

BEGIN

----- Lower section: ------

PROCESS (reset, clock)

BEGIN

IF (reset='1') THEN

pr state <= state0;

ELSIF (clock'EVENT AND clock='1') THEN

pr state <= nx state;</pre>

END IF;

END PROCESS;

----- Upper section: -----

PROCESS (input, pr state)

CASE pr state IS

WHEN state0 =>

IF (input = ...) THEN

output <= <value>;

nx state <= state1;

ELSE ...

END IF:

WHEN state1 =>

IF (input = ...) THEN

output <= <value>;

nx state <= state2;

ELSE ...

END IF;

WHEN state2 =>

IF (input = ...) THEN

output <= <value>;

nx state <= state3;

ELSE ...

END IF:

END CASE;

END PROCESS:

END <arch name>;

```

#### FSM template #1

- The flip-flops are in the lower section, so clock and reset are connected to it.

- The other lower section's input is nx\_state (next state), while pr\_state (present state) is its only output.

- The circuit of the lower section is sequential, so a PROCESS is required.

```

LIBRARY ieee;

USE ieee.std_logic_1164.all;

ENTITY <entity name> IS

PORT ( input: IN <data type>;

reset, clock: IN STD LOGIC;

output: OUT <data type>);

END <entity name>;

ARCHITECTURE <arch name> OF <entity name> IS

TYPE state IS (state0, state1, state2, state3, ...);

SIGNAL pr state, nx state: state;

BEGIN

----- Lower section: -----

PROCESS (reset, clock)

BEGIN

IF (reset='1') THEN

pr state <= state0;</pre>

ELSIF (clock'EVENT AND clock='1') THEN

pr state <= nx state;</pre>

END IF;

END PROCESS;

----- Upper section: ------

PROCESS (input, pr state)

CASE pr state IS

WHEN state0 =>

IF (input = ...) THEN

output <= <value>;

nx state <= statel;</pre>

ELSE ...

END IF:

WHEN state1 =>

IF (input = ...) THEN

output <= <value>;

nx state <= state2;

ELSE ...

END IF;

WHEN state2 =>

IF (input = ...) THEN

output <= <value>;

nx state <= state3;

ELSE ...

END IF:

END CASE;

END PROCESS;

END <arch name>;

```

## FSM template #1

Here is some typical code for the lower section:

```

PROCESS (reset, clock)

BEGIN

IF (reset='1') THEN

pr_state <= state0;

ELSIF (clock'EVENT AND clock='1') THEN

pr_state <= nx_state;

END IF;

END PROCESS;</pre>

```

- It has an, asynchronous reset, which determines the initial state of the system (state0),

- ... Followed by the synchronous storage of nx\_state (at the positive transition of clock), which will produce pr\_state at the lower section's output.

```

LIBRARY ieee;

USE ieee.std logic 1164.all;

ENTITY <entity name> IS

PORT ( input: IN <data type>;

reset, clock: IN STD LOGIC;

output: OUT <data type>);

END <entity name>;

ARCHITECTURE <arch name> OF <entity name> IS

TYPE state IS (state0, state1, state2, state3, ...);

SIGNAL pr state, nx state: state;

BEGIN

----- Lower section: -----

PROCESS (reset, clock)

BEGIN

IF (reset='1') THEN

pr state <= state0;</pre>

ELSIF (clock'EVENT AND clock='1') THEN

pr state <= nx state;</pre>

END IF;

END PROCESS;

----- Upper section:

PROCESS (input, pr state)

CASE pr state IS

WHEN state0 =>

IF (input = ...) THEN

output <= <value>;

nx state <= state1;

ELSE ...

END IF:

WHEN state1 =>

IF (input = ...) THEN

output <= <value>;

nx state <= state2;

ELSE ...

END IF;

WHEN state2 =>

IF (input = ...) THEN

output <= <value>;

nx state <= state3;

ELSE ...

END IF:

END CASE;

END PROCESS:

END <arch name>;

```

#### FSM template #1

- The upper section is fully combinational, so its code does not need to be sequential; concurrent code can be used as well.

- The CASE statement plays a the central role.

- This code does two things: (a) it assigns the output value and (b) it establishes the next state.

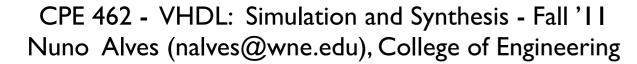

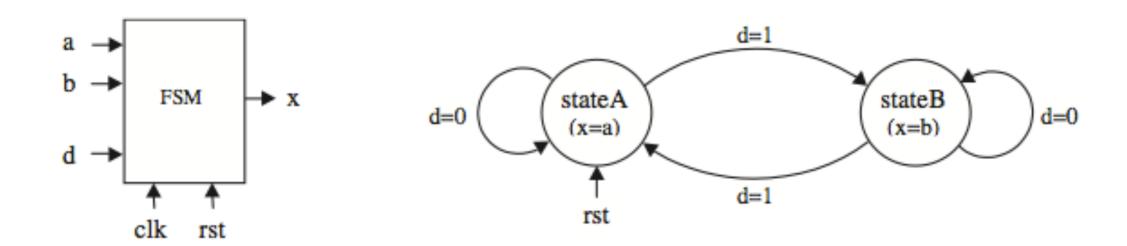

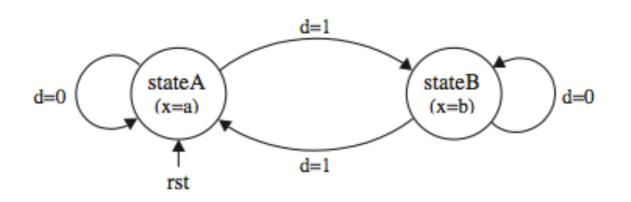

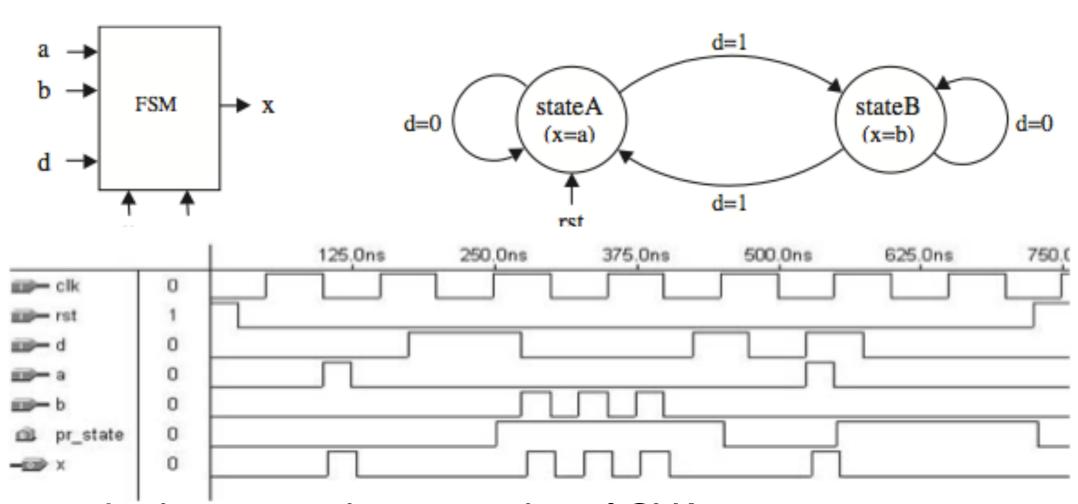

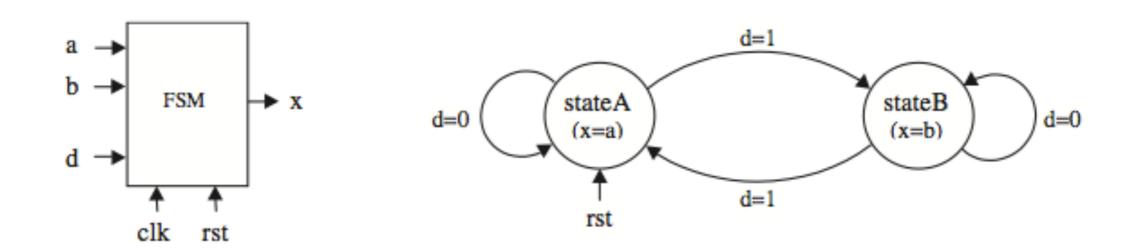

#### Example #2: Simple FSM

- The system has two states (stateA and stateB), and must change from one to the other every time d = 'I' is received.

- The desired output is x=a when the machine is in stateA, or x=b when in stateB. The initial (reset) state is stateA.

#### Implemented using FSM template #1

```

ENTITY simple fsm IS

PORT ( a, b, d, clk, rst: IN BIT;

x: OUT BIT);

END simple_fsm;

ARCHITECTURE simple fsm OF simple fsm IS

8

TYPE state IS (stateA, stateB);

SIGNAL pr_state, nx_state: state;

10 BEGIN

11

---- Lower section: ------

PROCESS (rst, clk)

12

13

BEGIN

14

IF (rst='1') THEN

pr state <= stateA;</pre>

15

16

ELSIF (clk'EVENT AND clk='1') THEN

17

pr state <= nx state;</pre>

18

END IF;

19

END PROCESS;

----- Upper section: -----

20

21

PROCESS (a, b, d, pr_state)

22

BEGIN

23

CASE pr_state IS

24

WHEN stateA =>

25

x \le a;

26

IF (d='1') THEN nx state <= stateB;</pre>

27

ELSE nx state <= stateA;</pre>

28

END IF;

29

WHEN stateB =>

30

x \le b;

```

#### Example #2: Simple FSM

- State only changes on the rising edge of CLK

- The output (x), which in this case **does** depend on the inputs (a or b, depending on which state the machine is in), varies when a or b vary, regardless of clk.

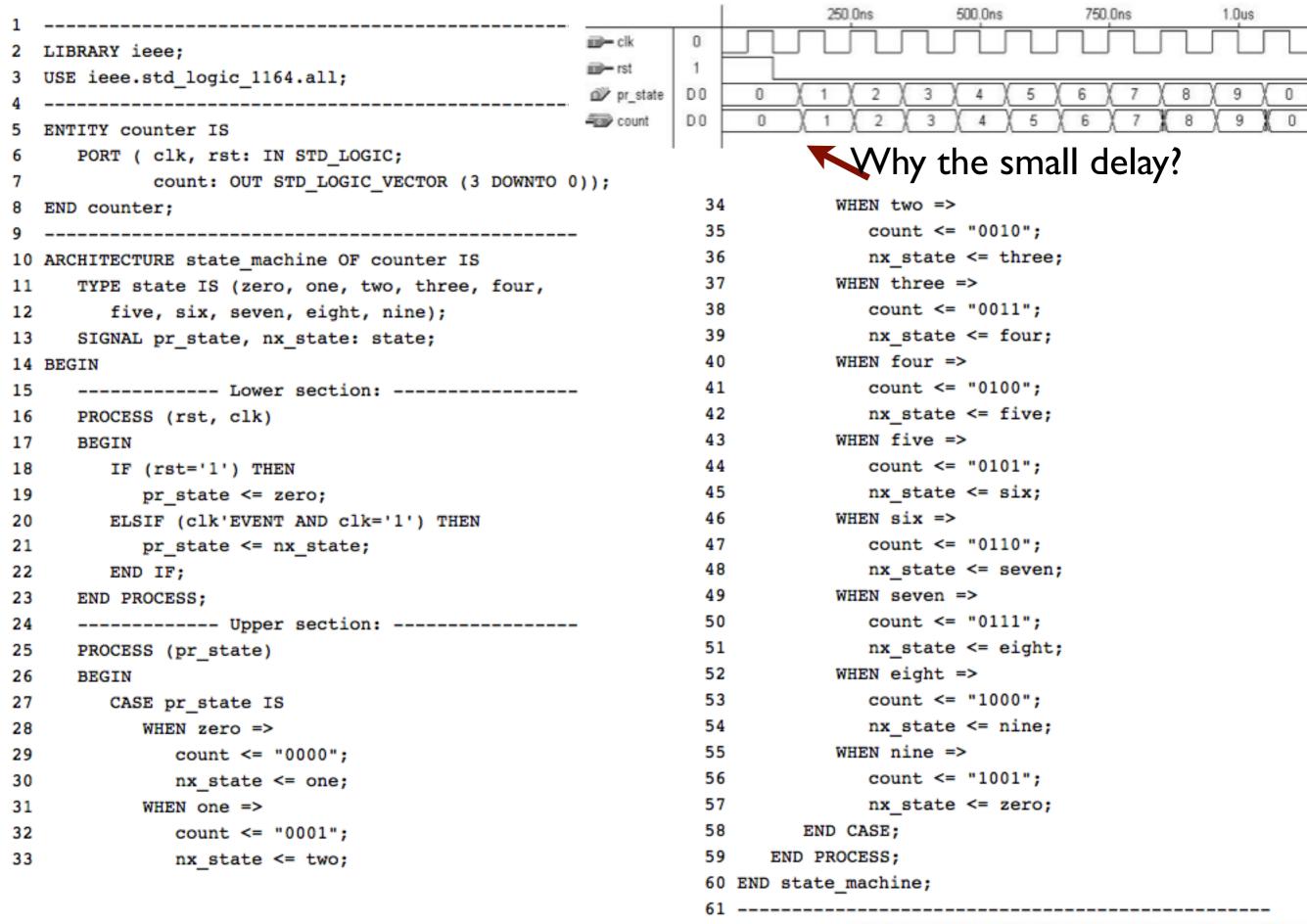

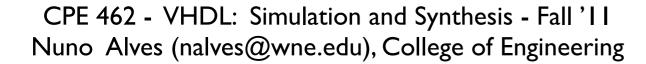

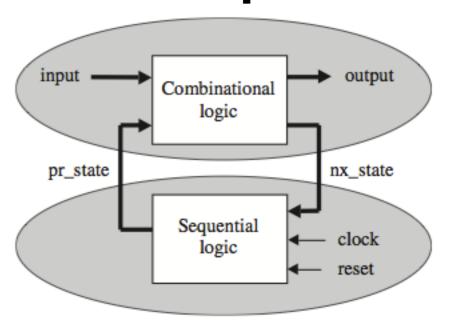

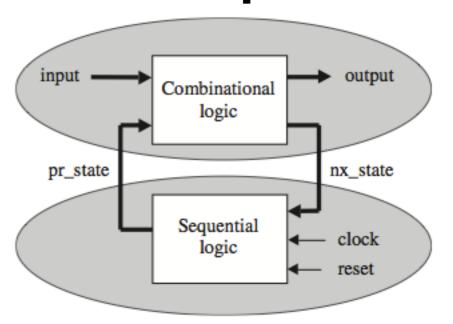

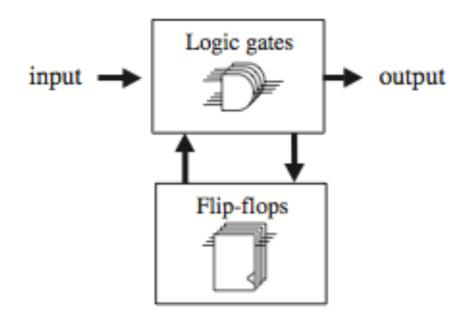

## Using FSM template #1

- In FSM template #1 only pr\_state is stored.

- Therefore, the overall circuit can be summarized as follows:

Notice that in this case the output might change when the input changes (asynchronous output).

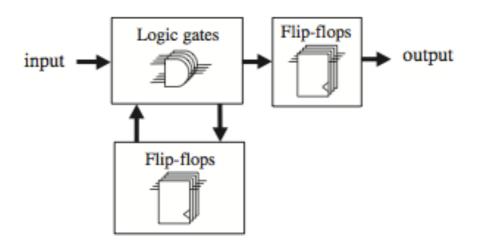

## What if we want a synchronous output?

- In many applications, the signals are required to be synchronous, so the output should be updated **only** when the proper clock edge occurs.

- To make FSM machines synchronous, the output must be stored as well.

• This is the goal of the FSM template #2.

```

LIBRARY ieee;

USE ieee.std logic 1164.all;

ENTITY <ent name> IS

PORT (input: IN <data type>;

reset, clock: IN STD LOGIC;

output: OUT <data type>);

END <ent name>;

ARCHITECTURE <arch name> OF <ent name> IS

TYPE states IS (state0, state1, state2, state3, ...);

SIGNAL pr state, nx state: states;

SIGNAL temp: <data type>;

BEGIN

----- Lower section: ------

PROCESS (reset, clock)

BEGIN

IF (reset='1') THEN

pr state <= state0;</pre>

ELSIF (clock'EVENT AND clock='1') THEN

output <= temp;

pr state <= nx state;

END IF;

FSM output is here

END PROCESS:

----- Upper section:

PROCESS (pr state)

BEGIN

Storing a temp!

CASE pr state IS

WHEN state0 =>

temp <= <value>;

IF (condition) THEN nx_state <= state1;</pre>

END IF;

WHEN state1 =>

temp <= <value>;

IF (condition) THEN nx state <= state2;</pre>

END IF;

WHEN state2 =>

temp <= <value>;

IF (condition) THEN nx state <= state3;</pre>

END IF;

END CASE;

END PROCESS;

END <arch name>;

```

## FSM template #2

Where output is **ONLY** updated only at a rising clock edge

- Very few modifications from template #1 are needed.

- For example, we can use an additional signal (say, temp) to compute the output value (upper section), but only pass its value to the actual output signal when a clock event occurs (lower section).

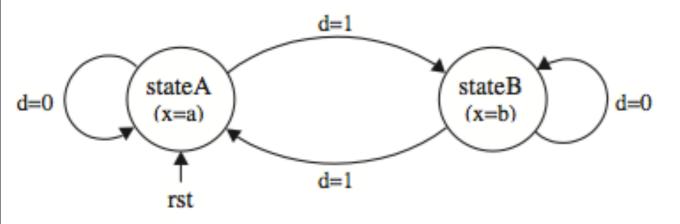

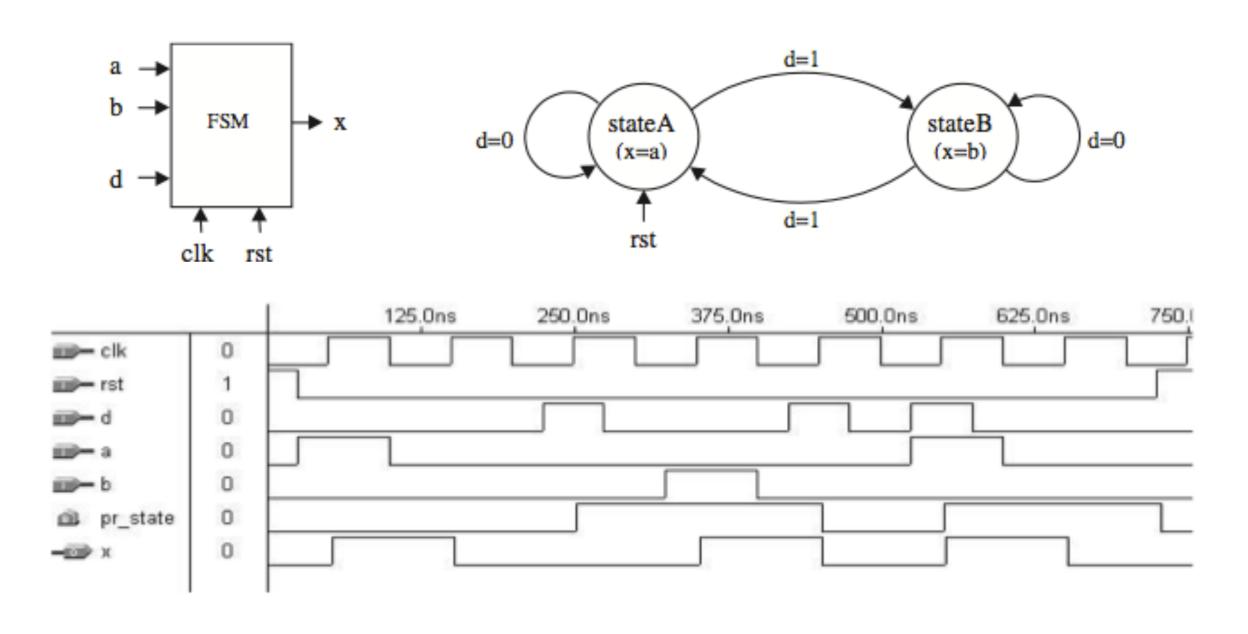

# Example #3: Simple FSM whose output only changes on a rising clock!

- The system has two states (stateA and stateB), and must change from one to the other every time d = 'I' is received.

- The desired output is x=a when the machine is in stateA **and** on a rising clock edge, or x=b when in stateB **and** on a rising clock edge. The initial (reset) state is stateA.

• If the input (a or b) changes during between two consecutive clock edges, the change might not be observed by the circuit; moreover, when observed, it will be delayed with respect to the input.

```

11 BEGIN

12

---- Lower section: -----

13

PROCESS (rst, clk)

14

BEGIN

15

IF (rst='1') THEN

16

pr state <= stateA;</pre>

ELSIF (clk'EVENT AND clk='1') THEN

17

18

x \le temp;

19

pr state <= nx state;

20

END IF;

21

END PROCESS;

22

----- Upper section: -----

23

PROCESS (a, b, d, pr state)

24

BEGIN

25

CASE pr_state IS

26

WHEN stateA =>

27

temp <= a;

28

IF (d='1') THEN nx state <= stateB;</pre>

ELSE nx state <= stateA;</pre>

29

30

END IF;

31

WHEN stateB =>

32

temp <= b;

IF (d='1') THEN nx_state <= stateA;</pre>

33

34

ELSE nx state <= stateB;

35

END IF;

36

END CASE;

37

END PROCESS;

38 END simple fsm;

```

#### Example #3: Simulation

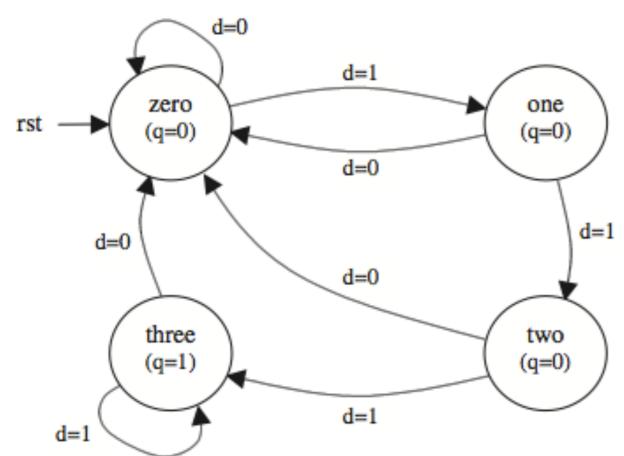

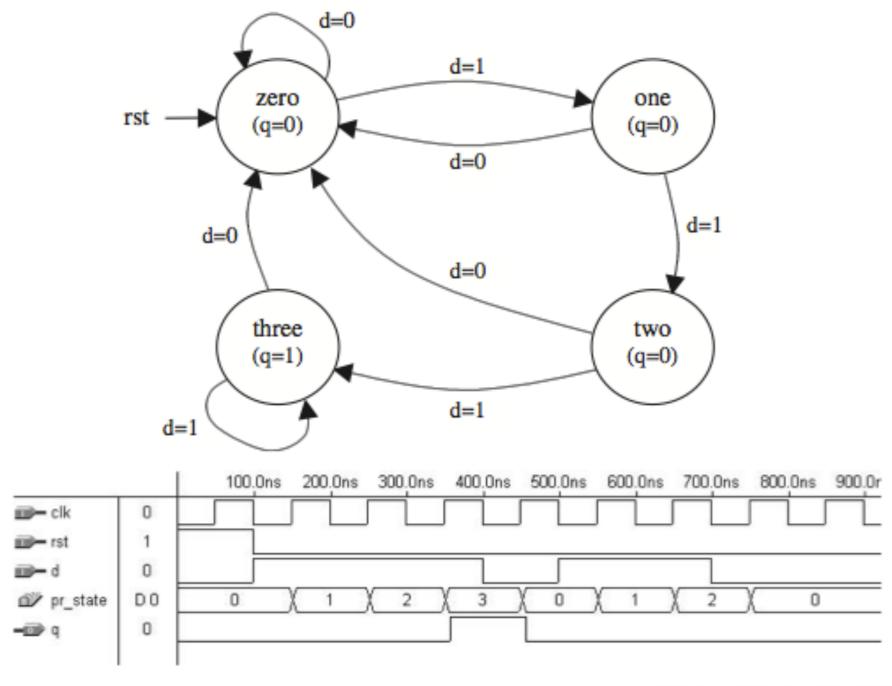

## Example #4: String detector

We want to design a circuit that takes as input a serial bit stream and outputs a 'l' whenever the sequence "III" occurs.

Overlaps must also be considered, that is, if ... 0111110 ... occurs, than the output should remain active for three consecutive clock cycles.

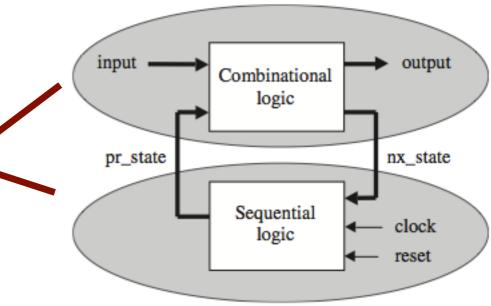

There are four states, which we called zero, one, two, and three, with the name corresponding to the number of consecutive 'I's detected.

```

LIBRARY ieee;

USE ieee.std logic 1164.all;

ENTITY string detector IS

PORT ( d, clk, rst: IN BIT;

q: OUT BIT);

END string detector;

10 ARCHITECTURE my arch OF string detector IS

11

TYPE state IS (zero, one, two, three);

SIGNAL pr state, nx state: state;

13 BEGIN

14

---- Lower section: -----

15

PROCESS (rst, clk)

16

BEGIN

17

IF (rst='1') THEN

18

pr state <= zero;</pre>

19

ELSIF (clk'EVENT AND clk='1') THEN

20

pr state <= nx state;</pre>

21

END IF;

END PROCESS;

22

d=1

zero

one

(q=0)

(q=0)

d=0

d=1

d=0

d=0

three

two

(q=0)

(q=1)

d=1

d=1

```

```

23

----- Upper section: -----

24

PROCESS (d, pr state)

BEGIN

25

26

CASE pr state IS

27

WHEN zero =>

28

q \le '0';

IF (d='1') THEN nx state <= one;</pre>

30

ELSE nx state <= zero;</pre>

31

END IF;

32

WHEN one =>

33

q \le '0';

IF (d='1') THEN nx state <= two;</pre>

34

35

ELSE nx state <= zero;</pre>

END IF;

37

WHEN two =>

38

q \le '0';

IF (d='1') THEN nx state <= three;</pre>

39

40

ELSE nx state <= zero;</pre>

41

END IF;

42

WHEN three =>

q <= '1';

43

IF (d='0') THEN nx state <= zero;</pre>

ELSE nx state <= three;

45

46

END IF;

47

END CASE;

48

END PROCESS;

49 END my arch;

```

Even if **d** changes, the upper section process will still use the **pr\_state** to make a decision. So, **q** will only change on rising edge.

#### Example #4: String detector

WESTERN NEW ENGLAND

UNIVERSITY